STE MEA

TREVENO

# BENEMERITA UNIVERSIDAD AUTONOMA DE PUEBLA FACULTAD DE CIENCIAS FISICO MATEMATICAS POSGRADO EN OPTOLECTRONICA

# THESIS

DEC 1 9 2000

E897/BTeV

"The Development of Software to Characterize the Fermilab Pixel Readout Chip for the BTeV experiment"

Submitted in satisfaction of the requirements for the Ph. D. in Physics with Specialty in Optoelectronics

Present

M. C. Maria Aurora Diozcora Vargas Treviño<sup>1</sup>

Advisor

Dr. Marleigh Sheaff<sup>2</sup>

# FERMILAB LIBRARY

## December 2000

FERMILAB-THES IS-2000-18

<sup>1</sup> Scholarship holder from CONACyT, MEXICO/Work developed in a stay at Fermilab, Batavia, III, USA <sup>2</sup> University of Wisconsin, Madison, USA/CINVESTAV, MEXICO

# ACKNOWLEDGEMENTS

I want to thank God for allowing me to be able to meet this enormous challenge in my life.

I want to express my most sincere acknowledgement to my husband Sergio Vergara Limon for all his help in the development of this work and for loving me so much, and to my daughters Teresita and Aurorita for their patience and love.

I want to acknowledge my parents Lic. Marciano Vargas Minor and Lic. Alejandra Concepcion Treviño Lopez, because for their help and love for me.

I whish to thank my advisor Marleigh Sheaff for all her help and advice during the curse of this project.

I whish to thank S. Zimmermann for advice during the course of this project and G. Chiodini for technical assistance. I also want to express my appreciation to the Fermilab staff and management, with special thanks to J. Appel, S. Kwan, and E. Barsotti. This work would not have been possible without the support and encouragement of A. Cordero and A. Fernandez of FCFM/BUAP. The support of the U.S. DOE and CONACyT, Mexico, is also gratefully acknowledged.

# TABLE OF CONTENTS

# INTRODUCTION

## **CHAPTER ONE**

| THE BTeV | EXPERIMENT AT FERMILAB |  |

|----------|------------------------|--|

|          |                        |  |

|                                          | 1      |

|------------------------------------------|--------|

| 1.1 The BTeV experiment                  | 3      |

| 1.2 Pixel plane                          | 5      |

| 1.3 Requirements for the Vertex Detector | ,<br>0 |

| 1.4 Conclusions                          | o      |

Page

1) ....

# **CHAPTER TWO**

# THE FPIX1 CHIP AND THE MULTI CHIP MODULE (MCM)

|                                                     | rage |

|-----------------------------------------------------|------|

| 2.1 The FPIX1 chip                                  | 9    |

| 2.1.1 Fermilab Pixel Chip 1                         | 9    |

| 2.1.2 Pad description and physical dimensions       | 15   |

| 2.1.3 Scan paths and Readout                        | 19   |

| 2.1.4 Design of patterns to control the FPIX1 chip. | 22   |

|                                                | Page |

|------------------------------------------------|------|

| 2.2 The Multi Chip Module (MCM)                | 24   |

| 2.2.1 High Density Interconnect Circuits (HDI) | 24   |

| 2.2.2 Operation of the MCM                     | 25   |

| 2.2.3 Design of patterns to control the MCM    | 27   |

| 2.3 Conclusions                                | 29   |

## **CHAPTER THREE**

### **CHARACTERIZATION**

|                                                                         | Page |

|-------------------------------------------------------------------------|------|

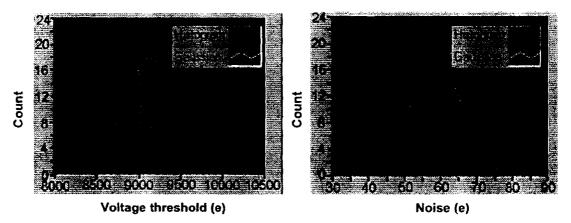

| 3.1 Bad pixel map test                                                  | 31   |

| 3.2 Threshold uniformity and noise tests without and with sensors on it | 31   |

| 3.3 Reproducibility                                                     | 33   |

| 3.4 Hit studies                                                         | 33   |

| 3.5 Test Setup                                                          | 33   |

| 3.6 Conclusions                                                         | 36   |

### **CHAPTER FOUR**

### SOFTWARE

| SOLIWARE                    | Page |

|-----------------------------|------|

| 1 The Laby IVW framework    | 38   |

| 4.1 The LabVIEW framework   | 40   |

| 4.2 Data Acquisition System | 54   |

| 4.3 Data Analysis System    | 60   |

| 4.4 General Flow Diagram    | 61   |

| 4.5 Conclusions             |      |

### **CHAPTER FIVE**

### **RESULTS OF THE CHARACTERIZATION**

|                                                                                  | Page       |

|----------------------------------------------------------------------------------|------------|

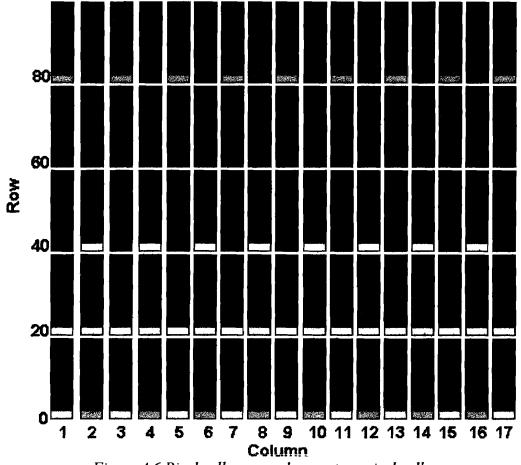

| 5.1 Bad pixel map                                                                | 62         |

| 5.2 Results of the single FPIX1 chip                                             | 63         |

| 5.3 Multi Chip Module (MCM) without sensors, threshold uniformity and noise test | 67         |

| 5.4 Multi Chip Module (MCM) with sensors, threshold uniformity and noise test    | 81         |

| 5.5 Reproducibility test                                                         | 8 <b>2</b> |

| 5.6 Hit studies                                                                  | 84         |

| 5.7 Other test developed on the MCM                                              | 85         |

| 5.8 Characterizing the MCM with its readout and control interface                | 90         |

|                     | Page |

|---------------------|------|

| 5.9 Conclusions     | 92   |

| GENERAL CONCLUSIONS | 93   |

|                     | 96   |

| DEFEDENCES          |      |

### REFERENCES

**APENDIX A**

SCHEMATIC OF THE SINGLE FPIX1 BOARD

## **APENDIX B**

SCHEMATIC OF THE MULTI CHIP MODULE (MCM)

## **INTRODUCTION**

High-energy physics is the science of the fundamental nature of matter. Studying subatomic particles and forces gives us a key to understanding the simple physical laws that govern the universe. In 1965, the United States Joint Committee on Atomic Energy (JCAE) and the National Academy of Sciences (NAS) approved a frontier high energy physics project to develop a 200 GeV Accelerator. In 1967, Robert R. Wilson was chosen by URA (Universities Research Association, Inc) as the first Director of the National Accelerator Laboratory (NAL). In 1974, the Laboratory was renamed in honor of Enrico Fermi as Fermi National Accelerator Laboratory. Physicists use accelerators of higher and higher energies to probe deeper and deeper inside the nucleus. Like a more powerful microscope, the higher and higher energy accelerators enable the investigation of smaller and smaller distances, by now even distances inside the proton. Higher energy accelerators also enable the production of heavier and rarer particles.

The search for new particles using the Fermilab accelerator produced a discovery in 1977, the first evidence for the bottom quark. Later on the first superconducting accelerator was constructed in the same tunnel as the original one, called the main ring. This new accelerator was later transformed into a proton-antiproton collider. The beam of particles begins as negative hydrogen ions in the Cockcroft-Walton accelerator. They continue to the Linac (Linear accelerator). As the beam of negative hydrogen ions enters the third accelerator, the circular Booster, both electrons are stripped off leaving a proton beam. Finally the protons are injected into the Main Ring. The antiproton source was essential to produce the proton's opposite particle. These antiprotons could then be steered into collision with protons and observed in specially designed detectors. The energy of these collisions would be close to 2 TeV in the center of mass. In 1985 the beam reached 800 GeV, and the first collisions of protons and antiprotons (combined energy of 1.6 TeV) were observed at the Colliding Detector at Fermilab (CDF). With the highest energy yet achieved the most powerful superconducting accelerator in the world the began the search for the most exotic particle within reach: the top quark. Two specialized detectors were constructed by large teams of experimenters at CDF and at DZero. In 1995 both the CDF and Dzero teams announced the top's discovery.

Under the command of John Peoples until 1999 and now under Michel Witherell the most powerful particle accelerator on earth, Fermilab's Tevatron, gives scientists from all over the United States and the world the opportunity to work together on experiments to try to understand the laws of nature. The Tevatron accelerates protons and antiprotons in a giant underground ring. When proton and antiproton collide at close to the speed of light, they make a tiny fireball of pure energy as intense as the big bang, when the universe was a trillionth of a second old. Some of the energy turns into matter, according to Einstein's famous equation,  $E = mC^2$ , yielding sprays of particles that may hold answers to our questions about the laws and origin of the universe.

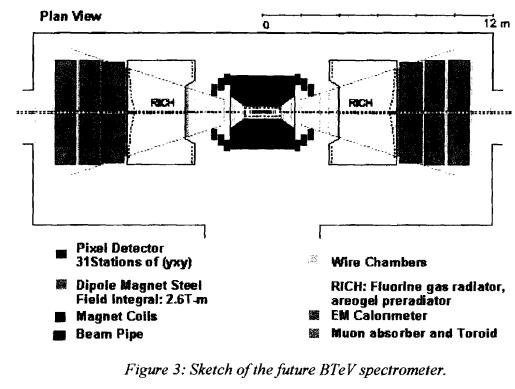

As the program at Fermilab moves forward the particle physics field focuses inside the quark and beyond. Fixed-target and colliding-beams experiments continue their searches on the frontier. In order to contribute to a deeper understanding of the heavy quarks, bottom and top. Fermilab has approved the BTeV experiment, E897. The new Fermilab's Tevatron will produce more than 400 billion b-flavored hadrons per year and 10 times as many c-flavored hadrons per year. A hadron is a particle made of strongly-interacting constituents (quarks and/or gluons). These include the mesons and baryons. Such particles participate in residual strong interactions. The heavy-flavored band a hadrons will be an excellent resource with which to investigate CP violation, quark/anti-quark mixing and rare decays. BTeV will be well positioned to answer the most crucial questions in heavy flavor physics. BTeV will use a powerful magnet, called SM3, which already exists at Fermilab. The other important parts of the experiment include the vertex detector, the RICH detectors, the EM calorimeters, and the muon system.

The pixel detector is a multi-plane pixel device that will sit inside the beam pipe. This silicon pixel detector has been proposed to be used in the first level trigger of the BTeV experiment. Thus, the BTeV pixel detector is central to the capability of the BTeV experiment. The major components for the pixel detector system will be the sensor, readout chip, sensor-to-readout-chip connection, mechanical support and cooling, high-density interconnection between the readout chips and the control chips on the detector plane peripheries, and the multiplexing and data transmission to the first-level trigger.

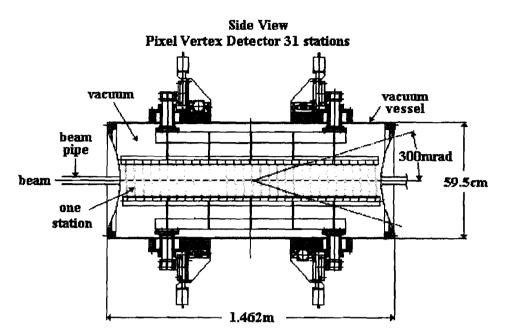

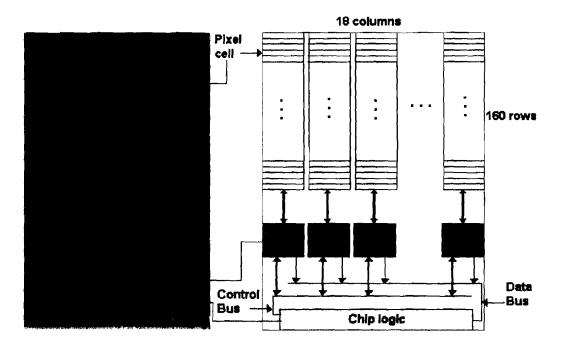

The silicon pixel detector will be composed of 62 pixel planes of 100x100mm each, divided into 31 stations with two planes each, placed perpendicular to the colliding beam and installed a few millimeters from the beam. VLSI pixel readout chips containing front-end electronics for every pixel sensor will be bump-bonded to the detector. Since this detector will be employed for on-line track finding for the lowest level trigger system, the pixel chip will have to read out all detected hits. The pixel chip development involves a succession of steps and submissions toward a chip that meets the BTeV requirements. VLSI chips with pixel unit cells of the same dimensions have been designed and built to instrument the sensors. The chips resulting from these steps have been dubbed FPIX0, FPIX1, and so on. The FPIX1 represents the first step towards the final pixel readout architecture. The FPIX1 chip is a column-based pixel chip with  $50 \,\mu m \times 400 \,\mu m$  pixel cells arranged in an array of 160 rows by 18 columns for a total of 2880 pixel cells. Current FPIX1 prototypes have sensitive areas of up to 59.2 mm<sup>2</sup>. In order to gain experience on the technical issues Fermilab has made a five-readout-chip sub-assembly with flexible cable interconnections, called the Fermilab multi chip module, or MCM.

Since each FPIX1 chip contains 2880 channels, and the experiment will use about 13000 chips, the task of characterizing them is challenging and potentially time consuming. We developed software within the LabVIEW framework to control a set of instruments to perform bad pixel map, threshold and noise tests on a full chip in a few hours of running. We also developed software to characterize the Fermilab Pixel module. My thesis work was performed as part of the research and development needed in order to build the pixel detector.

The main goal of the thesis is:

## "To develop a test stand including the test setup and software to characterize the Fermilab Pixel Readout chip (FPIX1) for the BTeV experiment"

In order to research the main goal of my thesis, we will describe as an abstract all the chapters containing in my thesis as follows:

In chapter one we give a brief explanation of the BTeV experiment. First we discuss the requirements of the experiment, explaining its goal. We also include a brief explanation of the parts of the experiment, e.g., the pixel detector.

In chapter two we describe the FPIX1 chip and the multi chip module (MCM). We give an extended explanation of how to handle and operate this chip. We give details on how we designed the patterns to control the chip in order to download and readout information from it. We show real photographs of the chip and also for the multi-chip module that contains five FPIX1 chips connected in daisy chain. As for the single FPIX1 chip we describe the correct way to download to and readout information from the MCM, describing all the signals that allow us to characterize it.

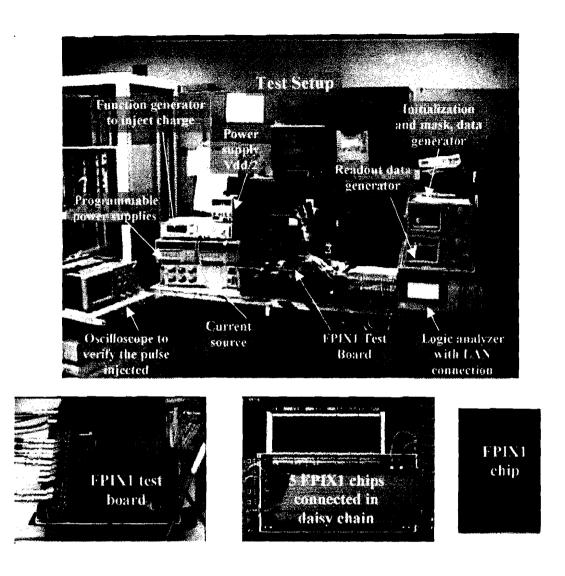

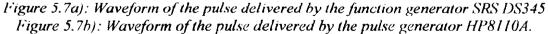

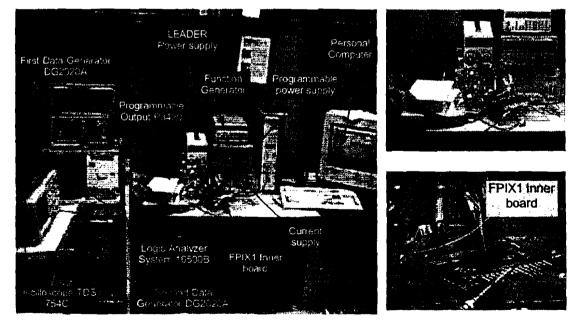

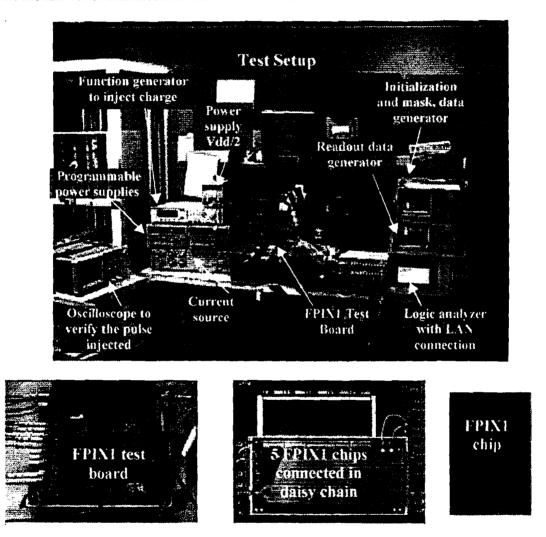

In chapter three we cover in detail the characterization of the FPIX1 chip, explaining the different tests that we performed on it, including the bad pixel map test, threshold uniformity test without sensors and with sensors bump-bonded to it, the reproducibility test, hit studies and other studies of interest. Later in this chapter we describe the test setup arranged to carry out all the characterization.

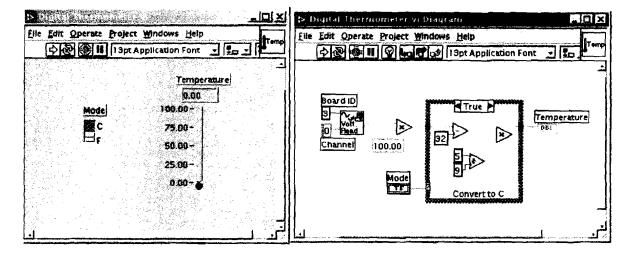

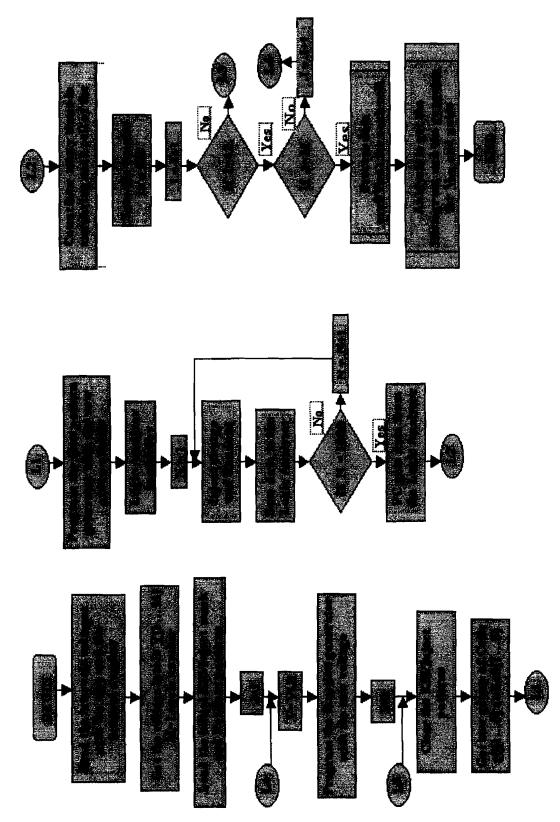

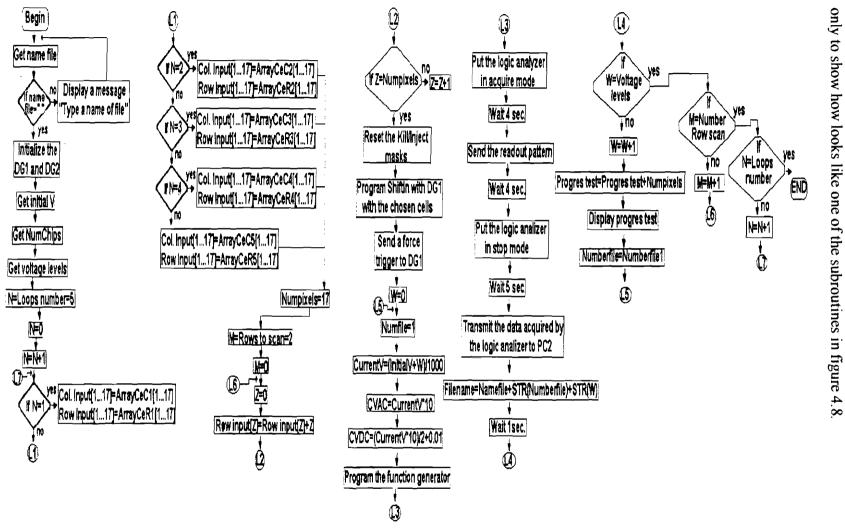

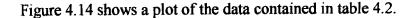

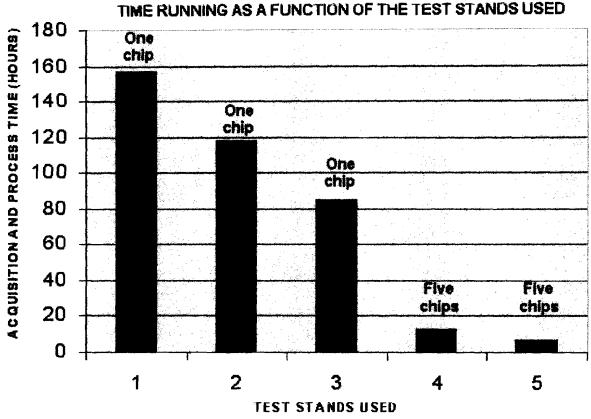

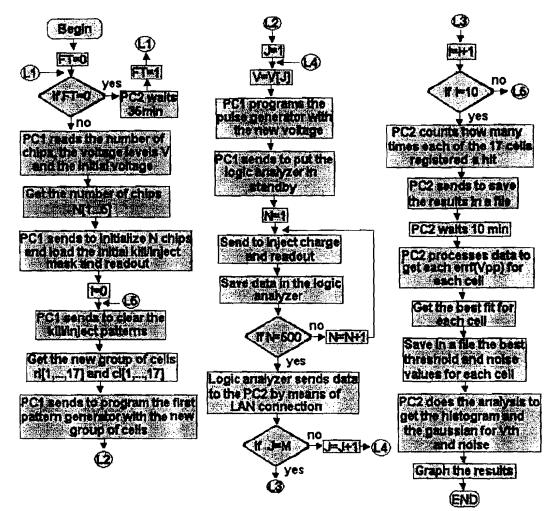

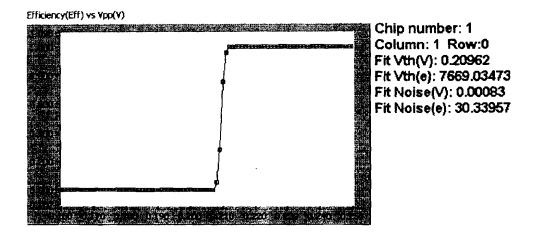

In chapter four we will describe the first test stand used (setup and software) to characterize the FPIX1 chips, which took about 157 hours (6.5 days) of running to characterize only one FPIX1 chip, which means 786 hours (32 days) of running to characterize 5 FPIX1 chips connected in daisy chain. The final version after an optimization of the test setup and software takes only 6 hours of running to characterize an MCM with 5 FPIX1 chips connected in daisy chain. And it could be possible decrease the running time injecting more than 17 cells at a time, because the most recently test using a computer with a 750 MHz processor speed shows that the process time is of only about 2 hours of running to characterize a MCM with 5 FPIX1 chips connected in daisy chain. Also, we show the development of the software used in the last version of the test stand. The software developed utilizes the LabVIEW (Laboratory Virtual Instrument Engineering Workbench) framework. LabVIEW is a development environment based on the graphical programming language G. It is integrated fully for communication with hardware such as GPIB, VXI, PXI, RS-232, RS-485, and plug in data acquisition boards. The software is a very important part of the tests, because it is by means of the software that we can control all the phases in the test. We describe the data acquisition system and the data processing system.

In chapter five we report the results obtained in the tests that we described in chapter three. Finally we give the references show and two appendices. As appendix A we show the layout and pin assignment for the single FPIX1 chip as mounted on the single-chip test board, and as appendix B, we show the layout and pin assignment of the multi chip module (MCM) assembly.

With the automatic characterization of the MCMs we are contributing to develop the first prototype of the half pixel plane for the BTeV Pixel Detector.

With this work we did the follow presentations and publications

#### Presentations:

- 1. M.A. Vargas, M. Sheaff, S. Vergara, "The development of software to characterize the fermilab pixel readout chip for the BTeV experiment", Poster presentation, SOMI XIV CONGRESO DE INSTRUMENTACION, Tonanzintla, Puebla, MEXICO 1999.

- 2. S. Zimmermann, S. Kwan, G. Cancelo, G. Cardoso, S. Cihangir, D. Christian, R. Downing, M. A. Vargas, et al., "Development of high data readout rate pixel module and detector hybridization at Fermilab", Poster presentation, PIXEL 2000, Genoa, June 2000.

- 3. G. Cancelo, S. Vergara, M.A. Vargas, et al., "Fiber optic based readout for the BteV's pixel detector", Poster presentation, LEB Sixth workshop on electronics for the LHC experiment, Cracow, Poland, September 2000.

#### Publications:

- 1. M.A. Vargas, M. Sheaff, S. Vergara, "The development of software to characterize the fermilab pixel readout chip for the BTeV experiment", Preceedings of the SOMI XIV CONGRESO DE INSTRUMENTACION, pp. 608-612, Tonanzintla, Puebla, MEXICO 1999.

- 2. M.A. Vargas, M. Sheaff, S. Vergara, "The development of software to characterize the Fermilab pixel readout chip, FPIX1, for the BTeV experiment", Accepted to NIMA, November 2000. Fermilab preprint FERMILAB-PUB-00-244E, November 2000.

- 3. S. Zimmermann, S. Kwan, G. Cancelo, G. Cardoso, S. Cihangir, D. Christian, R. Downing, M. A. Vargas, et al., "Development of high data readout rate pixel module and detector hybridization at Fermilab", Preceedings of the PIXEL 2000, Genoa, June 2000.

- 4. G. Cancelo, S. Vergara, M.A. Vargas, et al., "Fiber optic based readout for the BteV's pixel detector", Preceedings of the LEB Sixth workshop on electronics for the LHC experiment, Cracow, Poland, October 2000.

# **CHAPTER ONE**

### THE BTeV EXPERIMENT AT FERMILAB

The subject of the BTeV experiment is to learn more about the bottom and charm quarks. The experiment will use the Fermilab Tevatron. The accelerator will produce more than 400 billion b-flavored hadrons per year and 10 times as many c-flavored hadrons per year. These particles participate in residual strong interactions. The heavy flavored hadrons will be an excellent resource with which to investigate CP violation, quark/anti-quark mixing and rare decays. With all the results expected from the experiment, BTeV will be well positioned to answer the most crucial questions in heavy flavor physics.

### **1.1 THE BTeV EXPERIMENT**

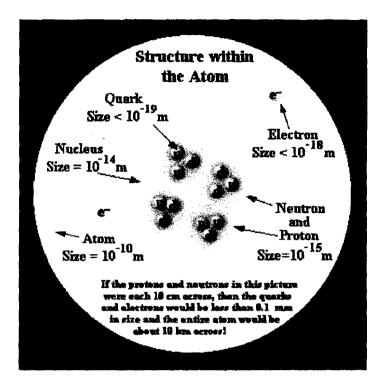

To understand better the subject of the BTeV experiment, we can see the atom's structure. The atom is know to contains many more elementary particles inside. The structure within the atom [1] is shown as Fig. 1.1.

Figure 1.1: The structure within the atom (this picture is a conception of an artist in a work made for Fermilab).

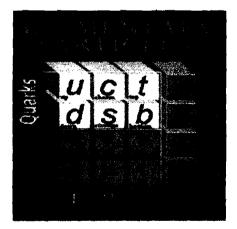

We can see that the neutrons and protons contain quarks. Also, inside the atom there are leptons. The elementary particles and force carriers [1] are shown in Fig. 1.2.

Figure 1.2: Elementary particles.

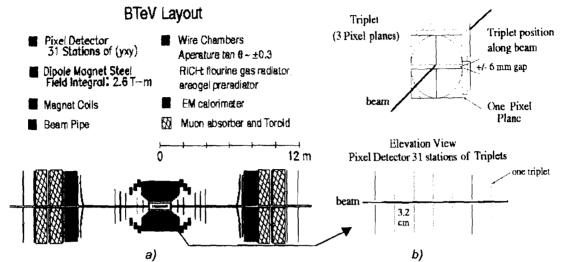

The BTeV experiments will use a powerful magnet, this magnet will generates 2.6 T-m. The other important parts of the experiment include the vertex detector, the RICH detectors, the EM calorimeters and the muon system [2]. A sketch of the future apparatus is shown as Fig.1.3.

The vertex pixel detector provides the high resolution space points near the interaction, which are used both online and offline to reconstruct tracks and associate them with their parent vertices. In designing the vertex tracking system, one must consider the long interaction region (IR) of the Tevatron, which has a  $\sigma_z = 30cm$ .

#### **1.2 PIXEL PLANE**

The BTeV experiment is going to use silicon pixel detectors because they provide high precision space points and they are quite radiation hard. Radiation hardness allows the detector elements to be placed very close to the beam approximately 6mm (in vacuum, separated from the beam only by a thin RF shield). The measurements of space points, with very little noise, provides superior pattern recognition, allowing the experiment to reconstruct tracks and vertices in real time, and trigger on events containing reconstructable heavy flavor decays. The long interaction region forces one to have a rather long vertex detector with many pixel planes.

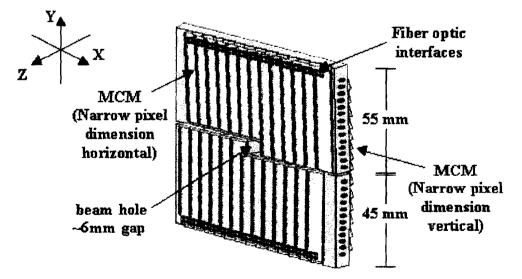

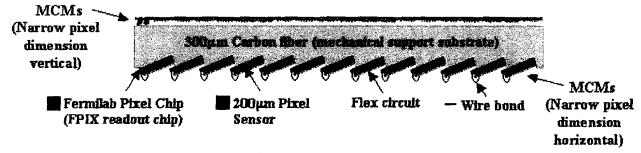

The pixel detector will contain about thirty million rectangular pixels, each 50  $\mu$ m X 400  $\mu$ m. Each pixel sensor is read out by a dedicated electronics cell. The pixel sensors are arranged in a bidimensional array, and the readout electronic cells are contained in a bidimensional array of unit cells of the same size as the sensors in the Fermilab pixel chip (FPIX). The two are connected by bump-bonds. The basic building block of the pixel vertex detector is a hybrid assembly called the Multi-Chip Module (MCM) which consist of a linear array of FPIX readout chips connected in daisy chain, bump-bonded to a sensor and wire bonded to a flexible printed circuit which carries I/O signals and power.

The baseline vertex detector will consist of a regular array of 31 "stations" of "planar" pixel detectors distributed along the interaction region, see Figure 1.4.

Figure 1.4: Side view of the future Pixel Vertex Detector, including the vacuum vessel and its mechanical support.

Each future station will contain one plane with the narrow pixel dimension vertical, and one with the narrow dimension horizontal, and is composed of two 5 cm X 10 cm halves. The half stations are mounted above and below the beam and are arranged so that a small square hole is left for the beams to pass through [2]. Two diagrams showing how the MCMs will be arranged on the pixel planes are shown in Fig. 1.5 and Fig. 1.6.

Figure 5: Future station composed by two 5 cm X 10 cm half stations. The station contains two planes, one plane with the narrow pixel dimension vertical, and the other with the narrow pixel dimension horizontal.

Figure 1.6: Future station top view.

The elementary charged particles generated by proton-antiproton collision will be bent by the magnetic field generated by means of the SM3 magnet. They will produce tracks in the pixel vertex detector. The curvature of a track will allow its momentum to be measured. Track will be used to from vertices. The RICH detector is made to use the *Čerenkov* effect to know the mass of these elementary particles. With this information many of the B particle decays will be able to be fully reconstructed.

### **1.3 REQUIREMENTS FOR THE BTeV VERTEX DETRECTOR**

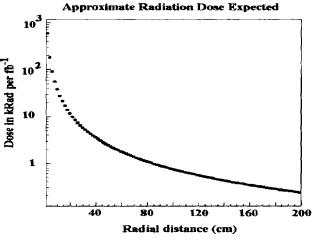

The BTeV experiment has very stringent requirements for the Pixel Vertex detector. The first constraint is that all the 31 stations must tolerate a high radiation dose. This dose has been calculated by people in the experiment. It depends on the radial distance from the beam, see Fig.1.7.

We can see from figure 1.7 that the FPIX chips near from the beam will receive about 1Mrad during one year of running and the electronics sitting on the perimeter of the pixels planes will receive about 100kRad.

Figure 1.7: Expected radiation dose at the Tevatron for one year running [3].

Another constraint associated with the pixel planes is their mass, they should be as light as possible to decrease particle interactions with the material. Strong interactions are the source of unwanted secondary particles. Electromagetic interactions and strong interactions causes scattering, which increases the error in the track's reconstruction [4]. The mean scattering angle (in milliradians) is approximately given by Eq. 1.1.

$$\Theta = \frac{13.6}{P} \sqrt{\frac{X}{X_0}}, \qquad (1.1)$$

where P is the momentum of the particle in GeV/c,  $X_0$  is the radiation length and X is the thickness of the material in question.

| Material        | $N_0$ (mm) |

|-----------------|------------|

| Water           | 360        |

| Beryllium       | 350        |

| Carbon fiber    | 250        |

| Beryllium oxide | 143        |

| Diamond CVD     | 123        |

| Silicon         | 100        |

| Aluminum        | 89         |

| Nickel          | 15.7       |

| Copper          | 14         |

| Silver          | 8.7        |

| Gold            | 3.4        |

Table 1 gives the radiation length of different materials.

Table 1: Radiation length of materials [4].

From Table 1 we can see that a particle traversing an aluminum sheet will have an approximately 2.5 times smaller mean scattering angle than in a copper sheet of same thickness.

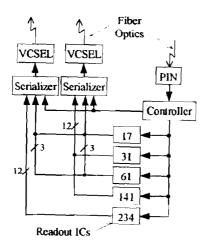

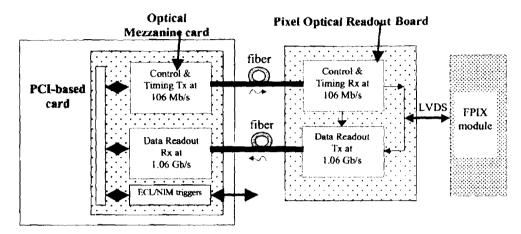

The experiment requires that the FPIX chips read out all detected hits. Since the pixel detector is used for the main first level trigger and the number of hits is quite large, it is necessary to provide significant readout bandwidth to transfer all data from the pixel chips to the trigger electronics. Simulations performed mapped the number of group hits per chip in a half plane [3], considering a pixel chip with active area of 8 mm X 8 mm ( $64mm^2$ ), each chip with 3200 pixels cells of  $50 \times 400 \mu m$ . The pixel chip uses 17 bits to deliver all the information about the position of a hit (row and column), time stamp, ADC and chip ID.

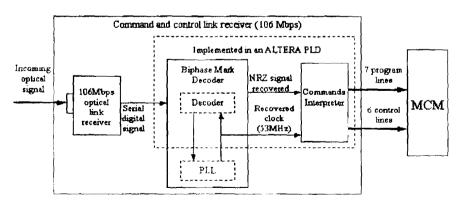

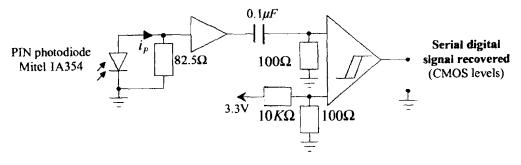

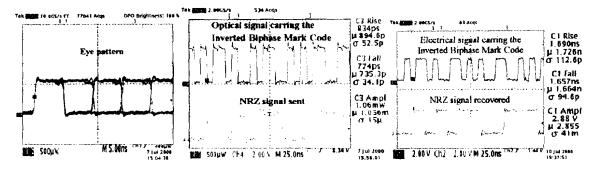

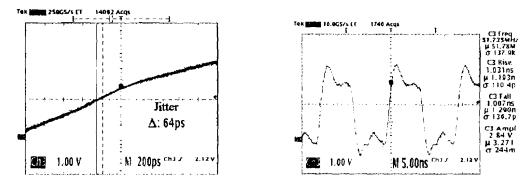

To achieve the high bandwidth required for the readout, ultra-high-speed digital optical links of 1-2 Gbps will be employed on each detector half-plane. A second type of digital optical link, which will send the command and control signals to the FPIX chips from the counting room to each detector half-plane, can operate at lower speed (~100 Mbps).

Both the emitters of the ultra-high-speed optical links and the receivers of the lower speed optical links will be about 7 cm from the beam if they are mounted on the detector planes as proposed in the baseline design. In this case, these devices will receive about 100 Krad of

radiation per year of running and will suffer some radiation damage. A further, rather stringent requirement is that they must operate inside the beam pipe in vacuum at  $\approx -5^{\circ}C$  [1]. Other solutions, which place the optical circuits outside of the vacuum vessel about 25 cm from the detector, are also being studied.

To satisfy all the BTeV requirements, the Pixel Vertex Detector will have all the properties shown in Table 2.

| Property                                           | Value                                          |

|----------------------------------------------------|------------------------------------------------|

| Picel size                                         | rectangular: 50 $\mu$ m × 400 $\mu$ m          |

| Plane Dimensions                                   | 10 cm × 10 cm                                  |

| Central Square Hole Dimensions (adjustable)        | nominal setting: 12 mm × 12 mm                 |

| Total Planes                                       | 62                                             |

| Total Stations                                     | 31                                             |

| Picel Orientations (per station)                   | one with narrow pixel dimension                |

|                                                    | vertical & the other with                      |

|                                                    | narrow dimension horizontal                    |

| Separation of Stations                             | 4.25 cm                                        |

| x-Plane to y-Plane Separation (within station)     | 5.0 mm                                         |

| Total Station Depth (incl cooling, supports)       | 6.5 mm                                         |

| Sensor Thickness                                   | 250 µm                                         |

| Readout Chip Thickness                             | 200 jan                                        |

| Total Station Radiation Length (incl RF shielding) | 2%                                             |

| Total Pixels                                       | $3 \times 10^{7}$                              |

| Total Silicon Area                                 | $\approx 0.6 \text{ m}^2$                      |

| Readout                                            | analog readout (3 bits)                        |

| Trigger                                            | signals are used in Level 1 trigger            |

| Rate Requirements                                  | time between beam crossings is 132 ns.         |

| Noise Requirement                                  | desired: $< 10^{-6}$ per channel/crossing      |

|                                                    | required: $< 10^{-3}$ per channel/crossing     |

| Resolution                                         | better than 9 µm                               |

| Radiation Tolerance                                | $> 6 \times 10^{14}$ particles/cm <sup>2</sup> |

| Power per Pixel                                    | <60 µWatt                                      |

| Operating Temperature                              | ~-5 °C                                         |

Table 2: Properties of the Pixel Vertex Detector.

-

### **1.4 CONCLUSIONS**

Until now we have a idea of the experiment and its requirements, now in the following chapter we will describe one of the principal integrated circuit which is one of the important parts of the pixel vertex detector, the FPIX1 chip. We will study the chip itself, describing the way to download and acquire information from it. Also we will describe the Multi-chip Module (MCM) that contains five FPIX1 chips connected in daisy chain that represent the first step to have a complete detector.

# **CHAPTER TWO**

## THE FPIX1 CHIP AND THE MULTI CHIP MODULE (MCM)

#### 2.1 THE FPIX1 CHIP

#### 2.1.1 Fermilab Pixel Chip 1 (FPIX1)

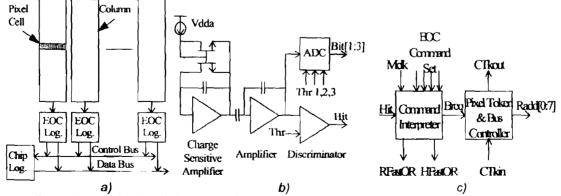

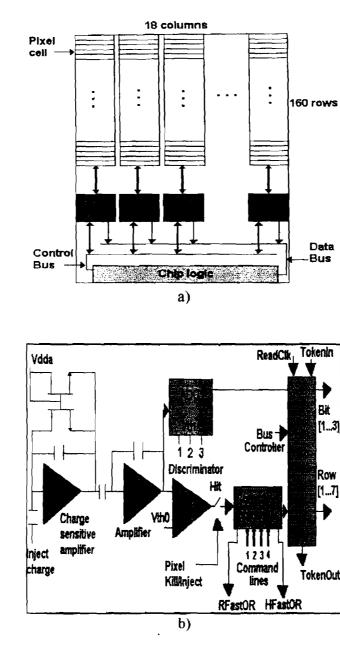

FPIX1 is the second in the sequence of submissions aimed at developing a chip that meets the BTeV requirements. It is a VLSI chip with pixel unit cells of size  $50 \mu m \times 400 \mu m$  arranged in an array of 160 rows by 18 columns for a total of 2880 pixel cells. The readout and control architecture is column based. The block diagram of the FPIX1 chip and a photograph of the chip are shown in Fig.2.1 [5]. The FPIX1 chip can be divided into three mutually dependent parts, the pixel cell, the End of Column (EOC) Logic and the Chip Control Logic.

Figure 2.1. FPIX1 Block Diagram

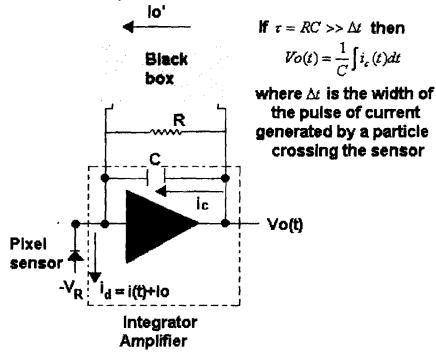

To better understand the front-end of the pixel cell we are going to analyze a basic front-end for a pixel sensor. A basic front-end contains a black box circuit, of which the purpose is to eliminate the effect of the leakage current on the integrator amplifier. This integrator amplifier is used to integrate the current generated when a charged particle crosses the pixel sensor. Then the signal output of the integrator amplifier will represent the charge produced by the particle crossing. The equations that result from an analysis of the basic front-end circuit are:

Figure 2.2 Basic front-end circuit.

Performing node analysis we obtain:

$$-[i(t) + lo] + lo' + i_c + i_R = 0$$

(2.1)

where i(t) is the current generated by the particle crossing, Io is the leakage current and Io' is the black box current. Then this equation can be divided in two cases the dc and the ac cases, for the dc case we have:

$$-Io + Io' = 0$$

;  $Io' = Io$  (2.2)

In consequence the current that flows by the black box must be equal to the leakage current denominated by *lo*. This condition is necessary and means that the leakage current doesn't flow thought the integrator amplifier. For the ac case we have:

$$-i(t) + i_c + i_R = 0; i_c = i(t) - i_R, \text{ or, } i(t) = i_c + i_R$$

(2.3)

and

$$i_c = C \frac{dVo(t)}{dt}; i_R = \frac{Vo(t)}{R}$$

(2.4)

where Vo(t) is the voltage output of the integrator amplifier. This voltage will be a pulse generated by the particle crossing. Taking the integral on both sides of the equation we have:

$$i(t) = \frac{dVo(t)}{dt} + \frac{Vo(t)}{RC}$$

(2.5)

Solving the differential equation we can obtain the natural response, setting the current i(t) equal to zero:

$$Vo_{n}(t) = Vo \exp\left(-\frac{t}{RC}\right)$$

(2.6)

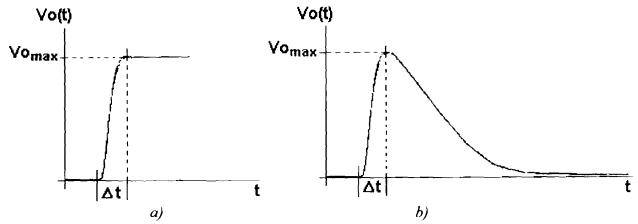

Then we can assume that the action of the resistor is to discharge the capacitor after the current generated by the particle crossing the sensor is integrated. If we don't put the resistance in the circuit then the capacitor always will be charged, i.e., if other particle crosses the sensor then the amplifier doesn't integrate the charge from zero. Instead the amplifier will begin to integrate the charge starting from the voltage level that has the capacitor, which is the level of the maximum voltage output of the amplifier produced by the first particle. With the incorporation of a resistance in the circuit we are avoiding this problem. For better understanding we show in figure 2.3 the shape of the integrator output without and with this resistance.

Figure 2.3 Shapes of the integrator output, a) without resistance and b) with resistance.

Following the analysis if  $\tau = RC >> \Delta t$  then the voltage output of the integrator amplifier will be:

$$Vo(t) = \frac{1}{C} \int i_c(t) dt$$

(2.7)

and how

$$Q(t) = \int i_c(t)dt = \int i(t)dt$$

(2.8)

where Q(t) represents the electrical charge as a function of time. This function will be a pulse generated by the particle crossing, resulting in the following relationship:

$$Vo(t) = \frac{1}{C}Q(t) \tag{2.9}$$

Then,

$Vo_{\max} = \frac{1}{C}Q_T \tag{2.10}$

where  $Vo_{max}$  is the maximum voltage of the pulse produced by the corresponding particle and  $Q_T$  is the total charge generated by the particle.

With this result we can see that there exists a relationship between the voltage output of the integrator amplifier and the charge collected by the sensor when a charged particle crosses it. Then we can see how important it is to characterize each front-end of a complete FPIX1 chip to assure a uniform response from cell to cell.

As an example we shown in the figure 2.4 a real signal obtained characterizing a front-end of the first prototype for the readout chip called FPIX0 [6]. The FPIX0 and the FPIX1 have essentially the same front-end electronics.

| File Qontrol Setup M  | casura Lilinia                        | i <b>Liteip</b> |           |    |

|-----------------------|---------------------------------------|-----------------|-----------|----|

|                       |                                       |                 |           | e  |

| <b>0</b> <sup>p</sup> | 9                                     | 当 <b>9</b> °    |           |    |

|                       | CONTRACTOR CONTRACTOR OF A MANAGEMENT |                 |           |    |

|                       |                                       |                 |           |    |

|                       |                                       |                 |           |    |

|                       |                                       |                 |           |    |

|                       |                                       |                 |           |    |

|                       |                                       |                 |           |    |

|                       |                                       |                 |           | 1  |

|                       |                                       |                 | 200 mc/Hz |    |

|                       |                                       |                 |           |    |

|                       |                                       |                 |           |    |

|                       |                                       |                 |           | 1  |

|                       | <b>M</b>                              | 12 <sup>6</sup> |           | £# |

Figure 2.4 A real signal obtained characterizing the front-end of the first prototype for the readout chip called FPIX0.

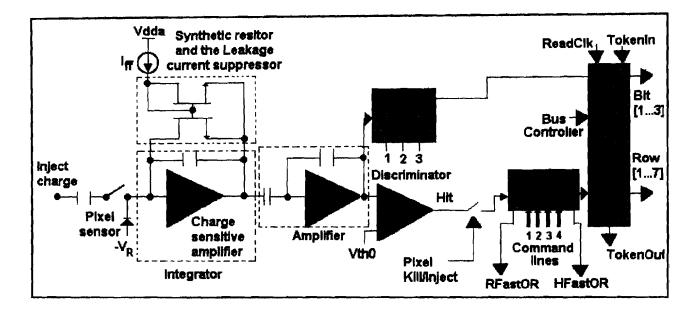

The Pixel cells hold the front-end (Fig. 2.5) electronics and the digital interface to the EOC logic. The front-end contains a charge-sensitive amplifier and a second amplification stage; the output of the second stage connects to a flash ADC and a discriminator. The discriminator output is asserted when the signal at the input of the discriminator is higher than the threshold (Vth0). The pixel cell contains a digital interface with two major components, the command interpreter and the pixel token and bus controller.

The command interpreter has four inputs corresponding to the four EOC command sets. These commands are presented by the EOC logic simultaneously to all pixel cell interpreters in a column. When an interpreter is executing the input command and the hit output from the discriminator is asserted, the interpreter associates itself with the particular EOC set and simultaneously it alerts the EOC logic to the presence of a hit via the wire-or'ed HfastOR signal. After that, the information is stored in the cell until EOC set issues an output or reset command. When this command is an output command, the interpreter issues a bus request and asserts the wire-or'ed RfastOR signal. Then the balance of the readout proceeds synchronously with the ReadClk. The EOC logic provides a column token, the token quickly passes pixel cells with no information until it reaches a cell that is requesting the bus. The data is composed of the ADC count bits [3:1] and the row address radd [7:0]. As the hit pixel is read out it automatically resets itself and withdraws its assertion of the RfastOR. This signal returns to its inactivated state while the rest of the hit pixels are being read out [5]. The action of the synthetic resistor is that it acts like a resistor for small signals and like a constant current source, discharging the feedback capacitor, for large signals.

Figure 2.5. Front End pixel cell.

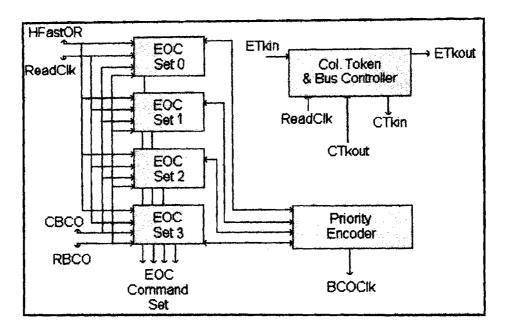

The end of column logic consists of a Priority Encoder and four EOC command set. The EOC command set consists of a timestamp register, a state machine to generate the EOC commands and two comparators. The priority encoder selects one EOC set to send a input command; when there is a hit in some pixel cell, the HFastOR signal is asserted and the state machine assign the EOC set. Then the EOC set responds by latching the current BCO (CBCO) in its EOC timestamp register, later on the EOC set send an idle command at the next rising edge of the BCO clock. With this feature all pixels in a particular column hit in the same clock period are associated with a single EOC set. The priority encoder assigns the next EOC set to send the input command to the column when the rising edge of the BCO clock is present.

We are not losing data in pixel cells in a column when there is a hit present in a column in up to four different crossings because the EOC logic has four EOC sets. When the EOC set is asserted it is waiting for matches with its stored timestamp BCO (SBCO). If this match is between the requested BCO (RBCO) and the SBCO, the EOC set broadcasts the output command and if the match is between CBCO and SBCO, it broadcasts the reset command. This defines the reset delay. A second machine is implemented inside the column token and bus controller. This second state machine is used to control the access to the EOC data bus; this access is arbitrated by an EOC token. When there is a match between the RBCO and the latched CBCO, the column controller issues the Ctkin token to the column and waits for the EOC Token In (ETkin) from the chip logic. When the ETkin is asserted, the column controller enables the pixel data onto the internal data bus and keeps it asserted until all the hits in the pixel cells in the column are reading out. The column controller now passes the EOC token to the next EOC logic by asserting ETkout. With the assertion of Etkout as soon as Ctkout is received by the column controller, we perform a full clock speed readout of the pixel data, even when the chip finishes the read out of one column and starts to read out the next. A scheme of the EOC logic is shown as Fig. 2.6.

Figure 2.6. End of Column Logic.

The chip control logic consists of the current BCO counter (CBCO), the readout BCO counter, a multiplexer and a chip controller, and controls the features associated with the whole chip. The CBCO increments synchronously with the BCOClk and then is delivered to the EOC logic. The multiplexer multiplexes the readout BCO counter or the external Request BCO (in case the external trigger is used); the output of the multiplexer forms the RBCO number that is delivered to the EOC logic. When the chip is operated in continuous readout mode, the multiplexer connects the Readout BCO counter to the RBCO, and this counter will provide the timestamp number that should be used to compare with the timestamp latched in the Timestamp registers. Other functions of the chip logic include external bus arbitration, which is done by a token passing from chip to chip. The configuration is programmed using a serial bit stream to set features like pixel cell kill (to disable pixels) and pulse inject select (for enabling programmable pixel cells to accept charge inject directly into the front-end using an external voltage source).

#### 2.1.2 Pad description and physical dimensions

The FPIX1 chip contains 87 pads. We show all the pads in the following tables [7].

| Function    | Pad number | Pad name | Description                             |

|-------------|------------|----------|-----------------------------------------|

|             | 1,87       | Vssa     | Pixel analog circuitry                  |

| ſ           | 9,79       | Vssd     | Pixel commands interpreters and drivers |

| Ground (0V) | 13,19,25   | Vsub     | Substrate voltage                       |

|             | 15,21      | Vssd-eoc | End of column Logic                     |

|             | 51         | Vss-pad  | Pad circuitry                           |

|             | 5,81       | Vss-comp | Pixel A to D conversion                 |

Twelve pads are providing ground:

Nine pads supplies power:

| Function     | Pad number | Pad name  | Description                             |

|--------------|------------|-----------|-----------------------------------------|

|              | 3,85       | Vdda      | Pixel analog circuitry                  |

| ) [          | 11,77      | Vddd      | Pixel commands interpreters and drivers |

| Power (3.3V) | 17,23      | Vddd-eoc  | End of column Logic                     |

|              | 53         | Vddd-pad  | Pad circuitry                           |

| f f          | 7,83       | Vddd-comp | Pixel A to D conversion                 |

One pad is the input for the charge injection:

| Function      | Pad number | Pad name | Description                  |

|---------------|------------|----------|------------------------------|

| Inject Charge | 2          | InjectIn | Analog input for test charge |

Six pads give the current bias:

| Function     | Pad number | Pad name  | Description                                     |

|--------------|------------|-----------|-------------------------------------------------|

|              | 4,10       | Ivbbnl    | Decoupling point and override for internal bias |

|              | 6          | Ivfb      | Feedback current (5nA)                          |

| Current bias | 8          | lvbbp     | Master bias current (7 $\mu$ A)                 |

|              | 12         | lvbbpl    | Decoupling point and override for internal bias |

|              | 14         | lvbb-comp | Decoupling point and override for internal bias |

Three pads are the threshold voltages for the ADC and one pad represents the threshold voltage of the discriminator:

| Function   | Pad number | Pad name | Description                        |

|------------|------------|----------|------------------------------------|

|            | 16         | Vth3     | Most significant threshold for ADC |

| Thresholds | 18         | Vth2     | Threshold for ADC                  |

| }          | 20         | Vth1     | Threshold for ADC                  |

|            | 22         | Vth0     | Threshold for hit comparator       |

Two pads are the bias voltage for the two different sensors i.e., p-stop and n-guard.

| Function     | Pad number | Path name | Description                           |

|--------------|------------|-----------|---------------------------------------|

| Bias voltage | 24         | Vpstop    | Bias voltage for the detector p-stop  |

|              | 26         | Vnguard   | Bias voltage for the detector n-guard |

| Function | Pad number | Pad name                          | Description                                   |

|----------|------------|-----------------------------------|-----------------------------------------------|

|          | 27/28      | TokenIn/TokenIn*                  | Input for the chip token                      |

|          | 29         | mode: Accept (3.3V) or reject (0V |                                               |

|          | 30         |                                   |                                               |

| Control  | 31         | DataRes                           | Reset signal                                  |

| signals  | 32         | ProgramRes                        | Reset signal                                  |

|          | 33         | ShiftClk                          | Shift clock signal                            |

|          | 34/35      | ReadCik*/ReadCik                  | The read out clock                            |

|          | 36/37      | BCOClk*/BCOClk                    | The beam cross over clock                     |

|          | 50         | LoadKill                          | Load kill pattern into pixels on falling edge |

|          | 76,78,80   | Reg2, Reg1, Reg0                  | Scan path selection bits (Reg2 is MSB)        |

Fifteen control signals, which we can program, control and readout the FPIX1 chip:

Thirty-two output signals

| Function               | Pad number | Pad name                  | Description                          |

|------------------------|------------|---------------------------|--------------------------------------|

|                        | 52         | ChipHasData               | Diagnostic path, it uses CMOS levels |

| 82 ShiftOut Output for |            | Output form scan path     |                                      |

| Output signals         | 38-49,     | Data outputs              | Data output signals                  |

|                        | 54-75      | (17 differential signals) |                                      |

|                        | 84/86      | TokenOut*/TokenOut        | Chip token output                    |

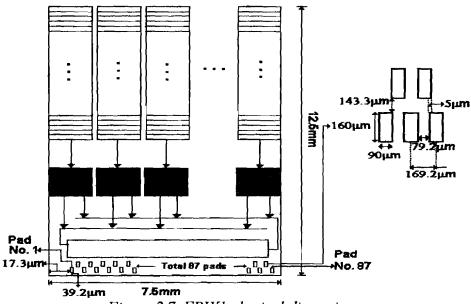

The size of the FPIX1 chip is 7.5mm by 12.5mm [4]. Pads 1 and 87 are 17.3 microns in from the outer edge of FPIX1. The bottom row of pads, which are the odd number pads, are 39.2 microns from the bottom of FPIX1. The FPIX1 pads are on a 169.2 micron pitch with 79.2 microns between pads, the pads themselves are 160 microns by 90 microns. A sketch is shown in fig. 9. A block diagram of the FPIX1 chip is shown as a Fig.2.7.

The most important signals are the control signals. With these signals we can download information to the chip. Most of these control signals are CMOS i.e., 3.3V represents a logical 1 and 0V represents a logical 0. The first control signals are Reg [2:0] that represent the scan path selectors for the ShiftIn signal; they are CMOS inputs. ShiftIn is a CMOS input for the scan paths. At the rising edge of the ShiftClk, the value at the ShiftIn will be scanned into the path chosen by the Reg0, Reg1, and Reg2 signals. ShiftClk is the clock signal; at the rising edge the contents of the ShiftIn signal are scanned into whatever scan path is selected by Reg0, Reg1, and Reg2 signals. DataRes is a reset level signal. When this signal is high, the BCO counters are reset to zero; the End of column registers are reset to empty and the chip stops outputting data. **ProgramRes** is a reset level signal. When this signal is high, the mask registers are set to zero; the chip is reset to continuous mode; the BCO lag is set to 2 and the ChipID is set to zero. LoadKill is the signal which latches the kill pattern that has been scanned into the pixel array on its falling edge. It is a CMOS level signal and it is kept at logical 1 during the kill scan, and dropped to a logical 0 to latch the kill pattern. TrigAcc is a dual-mode signal. If the chip is operating in triggered mode, it is the trigger signal. If the chip is operating in continuous mode, this pad is the Accept/Reject signal. In continuous mode, when this signal is logical 0 the chip rejects (ignores) incoming data, and when is logical 1 the chip accepts incoming data. This is a single ended CMOS signal.

To get the information acquired by the chip, we need to send the set of signals that control the readout of the chip information and then process it. Most of these signals are low voltage differential signals, or LVDS, (Vhi $\cong$  1.75V; Vlo $\cong$  1.55V). **ReadClk\*/ReadClk** is a free-running LVDS level differential clock. The simulated frequency was 26MHz, but the real frequency will be whatever the chip can handle. **BCOClk\*/BCOClk** is an LVDS representation of the beam crossover signal. **TokenIn/TokenIn\*** it is an LVDS input. When the signal is high (Pad 27=1.75V; Pad 28=1.55V), the chip can take the bus. When this signal is low (Pad 27=1.55V; Pad 28=1.75V), the chip cannot take the bus and its data outputs are tri-stated.

The ShiftOut represents the scan output for each of the scan paths selected by Reg0, Reg1 and Reg2. This signal is a CMOS level. This signal will be driven to the ShiftIn of the next chip when you connect several chips in daisy chain. TokenOut\*/TokenOut represents the output of the chip token signal.

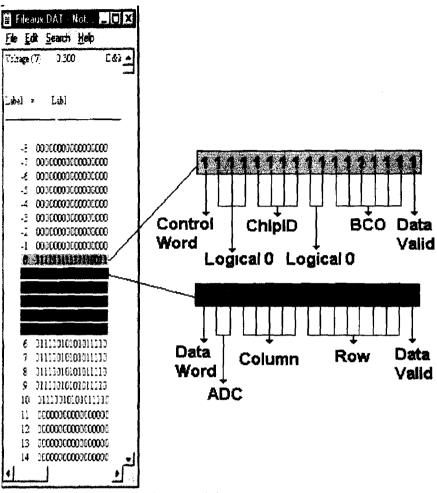

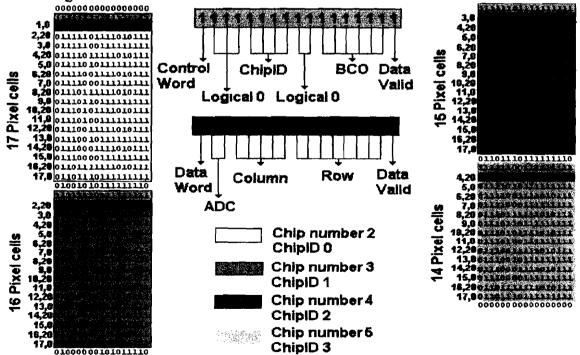

The FPIX1 chip delivers its information in the following data output format [7]. The data outputs are tri-statable LVDS outputs. Data 16 is the data valid signal; with this signal you can know if the chip has data to send. When the chip has data, the Data valid signal will be a logical 1 (3.3V) if there are no data this signal will be a logical 0 (0V). When there are data available, it will come in two forms i.e., control and data words; by means of Data 15 we can know whether the word presented is a control or a data word. Data 15 is a logical 0 in a control word and a logical 1 in a data word. The control word contains the ChipID of the chip and the BCO number (time stamp). The data word contains the row address, column address and magnitude (ADC value) of a particular hit pixel. In the table 2 we show all data and its corresponding meaning.

| Pad name         | Pads number | Data Available<br>Control Word | Data Available<br>Data Word |

|------------------|-------------|--------------------------------|-----------------------------|

| Data 16/Data 16* | 74/75       | Logicall                       | Logical1                    |

| Data 15/Data15*  | 73/72       | Logical 0                      | Logical 1                   |

| Data 14/Data 14* | 71/70       | Logical 0                      | ADC [1]                     |

| Data 13/Data 13* | 69/68       | Logical 0                      | ADC [0]                     |

| Data 12/Data 12* | 67/66       | Logical 0                      | Col Addr [4]                |

| Data 11/Data 11* | 65/64       | ChipID [0]                     | Col Addr [3]                |

| Data 10/Data 10* | 63/62       | ChipID [0]                     | Col Addr [2]                |

| Data 9/Data 9*   | 61/60       | ChipID [0]                     | Col Addr [1]                |

| Data 8/Data 8*   | 59/58       | ChipID [0]                     | Col Addr [0]                |

| Data 7/Data 7*   | 57/56       | Logical 0                      | Row Addr [7]                |

| Data 6/Data 6*   | 55/54       | Logical 0                      | Row Addr [6]                |

| Data 5/Data 5*   | 49/48       | BCO [5]                        | Row Addr [5]                |

| Data 4/Data 4*   | 47/46       | BCO [4]                        | Row Addr [4]                |

| Data 3/Data 3*   | 45/44       | BCO [3]                        | Row Addr [3]                |

| Data 2/Data 2*   | 43/42       | BCO [2]                        | Row Addr [2]                |

| Data 1/Data 1*   | 41/40       | BCO [1]                        | Row Addr [1]                |

| Data 0/Data 0*   | 39/38       | BCO [0]                        | Row Addr [0]                |

Table 2. Data outputs from the FPIX1 chip.

#### 2.1.3 Scan paths and Readout

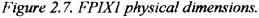

There are eight different control sequences by which we can download information to the FPIX1 chip. These are called scan paths and are formed by shift registers with different depths in the FPIX1. Shift registers are a type of sequential logic circuit, mainly used for the storage of digital data. They are a group of flip-flops connected in a chain so that the output from one flip-flop becomes the input of the next flip-flop. Most registers used in this way possess no characteristic internal sequence of states. All the flip-flops are driven by a common clock and all are set or reset simultaneously. A basic four-bit shift register can be constructed using four D flip-flops, as shown in Fig.2.8. The operation of the circuit is as follows. The register is first cleared, forcing all four outputs to zero. The input data is then applied sequentially to the D input of the first flip-flop on the left (FF0). During each clock pulse, one bit is transmitted from left to right. Assume a data word to be 1001. The least significant bit of the data has to be shifted through the register from FF0 to FF3.

To choose a particular scan path [7] we select one of the eight different codes using the control signals named **Reg0**, **Reg1**, and **Reg2**. For example to configure the chip, you must select the code 101. The codes are given in Table 3. To load all the scan paths into the chip, we are use the same **ShiftIn** pad, the same **ShiftClk** pad and the same **ShiftOut** pad. There is necessary time a relationship between **ShiftIn** and **ShiftClk** signals. **ShiftIn** must be delayed by more than 5ns from **ShiftClk**.

|   | Reg2, Reg1, Reg0 | Path                             |

|---|------------------|----------------------------------|

| 0 | 000              | Idle – No path                   |

| 1 | 001              | Trigger path                     |

| 2 | 010              | Not used                         |

| 3 | 011              | Programmable reset delay         |

| 4 | 100              | Not used                         |

| 5 | 101              | Configure (Mode, ChipID and Lag) |

| 6 | 110              | Kill or Inject                   |

| 7 | 111              | Kill or Inject                   |

Table 3. Scan paths to program the FPIX1 chip.

A brief description the register codes for selection of each of the scan paths is as follows: The idle path should be the default path, if no action is taken **Reg2**, **Reg1** and **Reg0** should be set to 000. The paths selected by 010 and 100 instruct the chip to take no action as for the idle path. The trigger path code is 001 and you select this if you want to use the chip in external trigger mode. This path is six bits deep, and the most significant bit is scanned in first. When all six bits have been scanned in, a pulse on the **TrigAcc** pin (pad 29) will produce a new trigger request to the end of column logic cells.

The code to select programmable reset delay path is 011. Each EOC logic circuit has a mask register that is six bits deep. When all the bits in the mask register are equal to zero the EOC logic will reset itself in 64 BCO clock cycles. When all bits in the mask register are set to one, the column is effectively shut down. This scan path is 102 bits long because each column has a 6 bits mask register in its EOC logic circuit, this means 6x17=102 bits. Then, e.g., you send 102 bits of zeros to do a reset delay by means of the ShiftIn pad. The most significant bit of column 17 is scanned in first; the least significant bit of column 1 is scanned in last.

The register code for the configure path is 101. This path is used to program the mode of operation of the chip, the identification number (ChipID) and the BCO lag number. There are two modes of operation, triggered mode or continuous mode. If you enter a logical 1 (3.3V) into the pattern you select triggered mode, while if you enter a logical 0 (0V) you select a continuous mode. The ChipID number is the identification number of the chip. If you are working with one chip, you can give it any identification number, e.g., 0000. If you have more than one chip, as on the MCM, you need to identify the chip from which you are receiving information. The BCO lag is the minimum distance between the current BCO number and the requested BCO number in continuous mode. Typically, this number is set to two. The configure path contains 11 bits, 1 bit for the mode of operation, 4 bits for the ChipID number and 6 bits for the BCO lag. Then, by means of the ShiftIn pad you need to send 11 bits with the configuration that you want. The most significant bit

of the BCO lag is scanned in first, followed by the rest of the BCO lag. Then the most significant bit of the ChipID is scanned in. Finally, the mode of operation is scanned in.

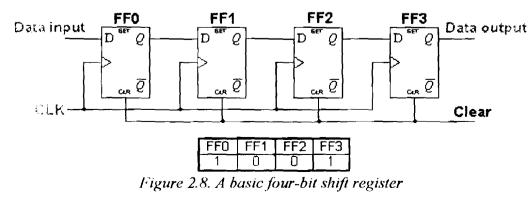

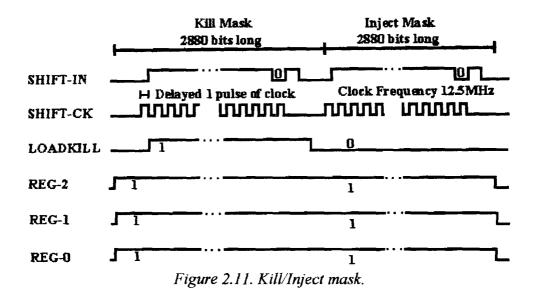

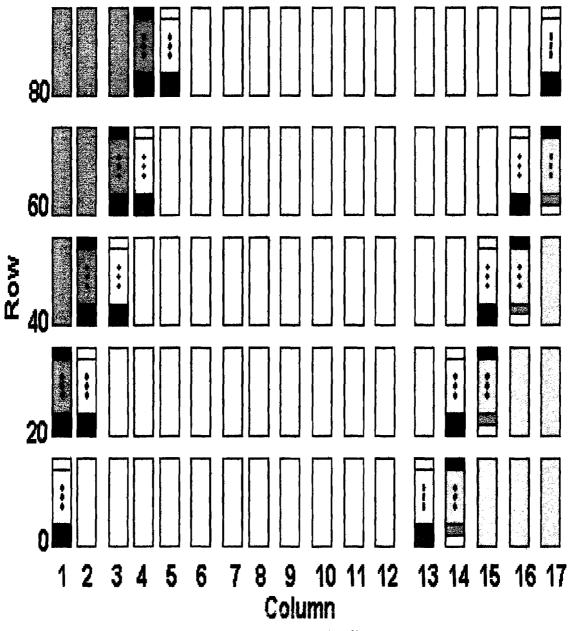

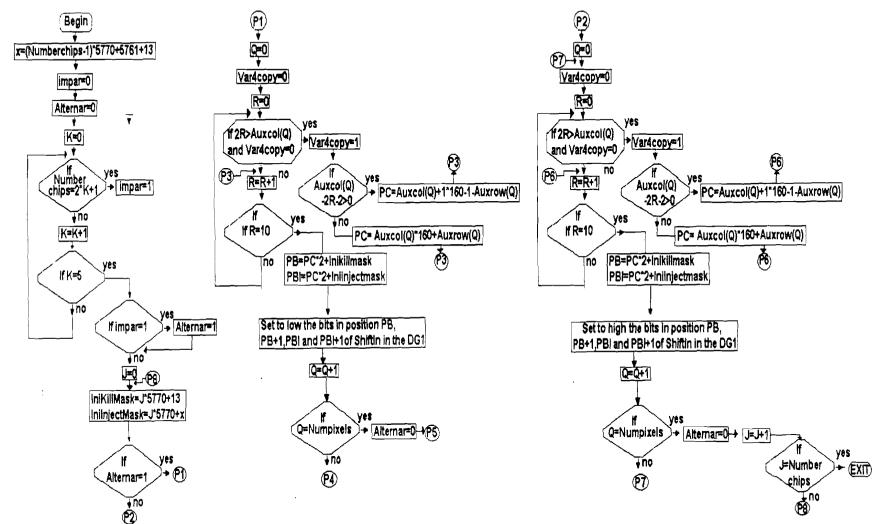

The codes for the kill/inject paths are 110 or 111. These paths select the pixel cells that you want to kill (disable) and the pixel cells which will be enabled for charge injection. In the FPIX1 chip we have 160 rows by 17 columns, for a total of 2880 pixel cells. The number of data bits we need to program the kill/inject path is 5760. The first 2880 bits form the kill mask, while the second 2880 bits represents the inject mask. During the loading of the kill mask the LoadKill signal (pad 50) should be held high, and for the inject mask this should be held low. The scan path starts at the lowest number pixel of the column  $17^{th}$  and goes up to the highest pixel in that column. From there the scan path continues to the highest pixel of column  $16^{th}$  and goes down to the lowest number pixel and goes up to the highest number pixel, and for even column the scan path starts in the highest number pixel and goes down to the lowest number pixel. This scan scheme is shown in Fig. 2.9. A logical 1 (3.3V) in the kill pattern means that the pixel is killed; a logical 0 (0V) in the inject pattern means that the pixel will be injected.

Figure 2.9. Kill/Inject Scan Path.

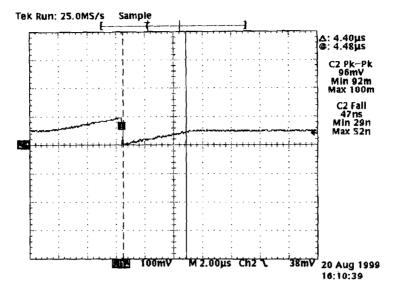

After you have selected a pixel cell to be enable (not kill) and to be injected with charge, you inject charge to the chip and then you must send a set of signals to the chip to read out the information that you have generated by means of the injection. These signals are: **DataRes**, **BCOCIk**, **ReadClk**, **TokenIn** and **TrigAcc**. All these signals except **DataRes** are LVDS levels. You can work with these signals as CMOS levels by supplying voltage to the terminal Vdd/2, which allow us to work in single-ended mode rather than differential. Following injection, if there is data on the bus, the Data Valid bit (Data 16) will be 1. The data will change at the falling edge of the **ReadClk**, and it will be stable at the next rising edge of the **ReadClk**. Therefore, the data lines [0:15] should be latched by the data acquisition system at the rising edge of the **ReadClk** when Data Valid is logical level 1. You need to send a **DataRes** resets the BCO counters, the End of column registers are reset to empty and the chip stop outputting data.

As all the cells on the FPIX1 chip use the same data bus, we control the bus access using the **TokenIn** signal. If you have, for example, N FPIX1 chips connected in daisy chain, the chip with the token can access the bus and transmit its own data. Then the **TokenOut** signal of chip N-1 is connected to the **TokenIn** signal of chip N. If the chip is to be used in single chip mode, its TokenIn can be set to a logical 1. Finally, the chip will accept hits if the TrigAcc signal is logical level 1, and will reject hits if this signal is logical level 0.

#### 2.1.4 Design of patterns to control the FPIX1 chip

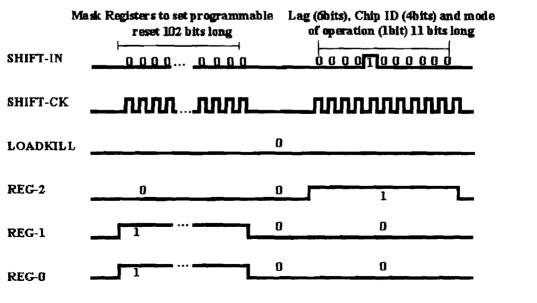

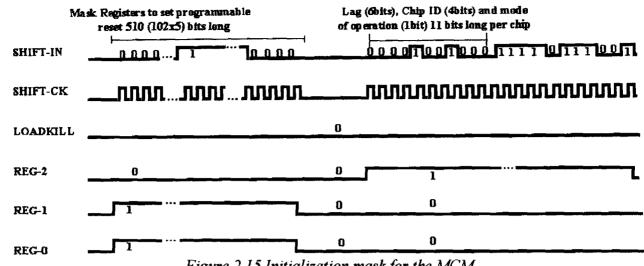

Now that we are familiar with the FPIX1 chip and its functions, we need to design the patterns we will use to download the information to control the chip and to read out the data generated by charge injection. The first set of information that we download to the chip is in an array of commands called initialization. This array contains all the commands to perform a reset and to set up the configuration. To do a reset we need to send the scan path code 011 (**Reg2=0**, **Reg1=1**, **Reg0=1**) and 102 bits of zero logic by means of the ShiftIn path. We also send the clock signal by the ShiftClk pad. This completes the reset. After a short delay we send the commands to configure the chip. For this, we select the scan path 101 (**Reg2=1**, **Reg1=0**, **Reg0=1**). In this mask we send the lag number equal to two, in the 6 BCO bits of the mask, the chip ID number in the 4 ChipID bits, and, the mode of operation in the 1 bit mode. This means that the mask is 11 bits long. A sketch of the FPIX1 chip initialization as seen in the screen of the data generator is shown in fig.2.10.

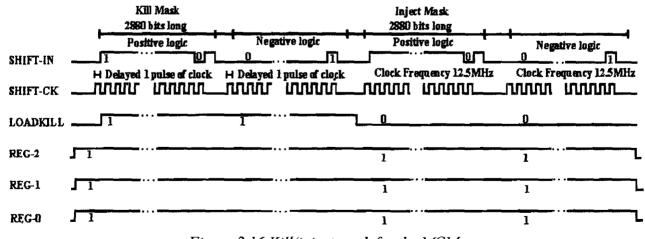

The next step is to send the kill/inject mask; selected by means of the path code 111 (**Reg2**=1, **Reg1**=1, **Reg0**=1) or 110. This mask activates the pixel cell or cells that we want to characterize. Sending a logic zero to a specific cell in the kill mask means it is enabled to receive charge on it, while sending a logic one means that it is disabled. In the inject mask a logic one represent that the pixel cell will not be injected and a logic zero means that it will. The kill mask is 2880 bits long, the inject mask is 2880 bits long. These bits correspond to the 2880 pixel cells that the FPIX1 contains. The shift-in is delayed by one pulse of clock from the shift-clock. The frequency of the shift-clock is 12.5MHz. The loadKill needs to be enabled during the kill mask and to be disabled for the inject mask. A sketch of the kill/inject mask as seen in the screen of the data generator is shown as Fig.2.11.

Figure 2.10. Initialization mask

Following initialization send a set of signals that inject charge and then performs the readout of the information that the chip delivers in response to the charge injection. These signals are the charge inject (**InjectIn**), the data reset (**DataRes**), the BCO clock (**BCOClk**), the readout clock (**ReadClk**), the token in (**TokenIn**) and the trigger accept (**TrigAcc**). All of these are included in a single mask in the correct time sequence. Before injecting charge you need to send a **DataRes** signal in order to clear stale information, e.g., from previous charge injection. **DataRes** causes the BCO counters to be reset, the End of column registers to be reset to empty and the chip to stop outputting data. We send the charge inject signal  $10\mu s$  after send the DataRes, by means of the pin marked **InjecIn**. At the same time we send two signals, Clockpod1 and Clockpod2, with which we synchronize the logic analyzer to accept all the data that the chip delivers. A sketch of the readout is shown in Fig. 2.12.

| INJCHAR  |                                                                                                                                                                                                                                   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATARES  | 15 pulses of clock to<br>read until 9 cells                                                                                                                                                                                       |

|          |                                                                                                                                                                                                                                   |

|          |                                                                                                                                                                                                                                   |

| BCO-CLK  |                                                                                                                                                                                                                                   |

| READ-CLK |                                                                                                                                                                                                                                   |

| TOKEN-IN | an a fair ann an                                                                                                                                                                                 |

| TRIGACC  | na († 1618), 1814 ap Brigger, fals Bladd Brigger Mauren, Frisk Brien († 1974), 1824 ap 1934 april 2014 ap 1934<br>An 17 - 1931 ap 1844 ap 1937 ap |

Figure 2.12. Readout mask.

### 2.2 THE MULTI CHIP MODULE (MCM)

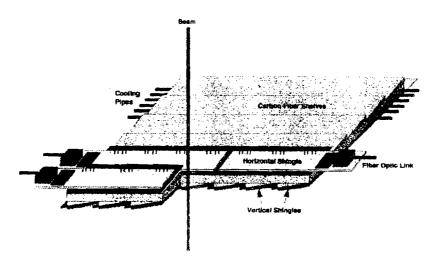

The innermost detector for the BTeV experiment will be a pixel detector. This detector will be composed by 62 pixel planes, and each plane contains several pixel chips bump bonded to the sensors. A very important constraint associated with these planes is their mass. They should be as light as possible to decrease particle interactions with the material. Particle interactions cause scattering and thus increase the error in the reconstruction of the trajectories of the particles. Other important constraints related to the pixel detector are that they must work in a high radiation environment and in vacuum. The detector will suffer a substantial radiation dose, which means that it has to be built with material and glues that are radiation hard. Also they cannot outgas or evaporate in vacuum. Since the detector is inside vacuum, most of the heat has to be conducted from the chips to liquid cooling channels placed in the support material. In this case carbon fiber structures are good candidates because they provide lower mass associated with good thermal conductivity and are none the less structurally sound. For all these reasons the experiment decided to glue high density interconnect (HDI) circuits on the top of a carbon fiber plate that holds the detector and associated electronics. The cooling channels are embedded in the plate and are also made from carbon that has been fused into glassy tubes. The readout and control chips will be wire bonded to the HDI.

#### 2.2.1 High Density Interconnect Circuits (HDI)

In the new world of electronics the HDI has gained a very high importance. The trend toward miniaturization and toward higher and higher speed devices has increased the demand for smaller and smaller semiconductor components with an even increasing density of input-output signals as well as a demand for a higher number of connection points on the printed circuit boards (PCB) on which the chips are mounted. Multi-layer flex circuits will provide the interconnection densities needed to meet the demands for the BTeV experiment.

The flex circuit contains four layers, two layers for signal interconnects, one layer for power and other signals and one layer for the ground plane [4]. There are two ways to proceed in order to produce the flex circuit. One is to use a four circuit layer flex circuit, and the other is to use two flex circuits, each with two layers and one assembled on the top of the other. Other approaches can also be considered, like one with two flex circuits with differing densities, one assembled on the top of the other. This idea is based on the fact that just portion of the circuit requires high density interconnect. The first circuit would be two layer flex circuit layout using "standard" design rules (with 100µm minimum traces and spaces widths, 400µm via cover pads and 200µm via through holes). The second flex, which would be built using more "aggressive" design rules (like 25µm traces widths and 68µm via cover pads), is used for the signal interconnects. In our application, this two rule flex circuit could be employed in the following way: the "standard" rule circuit would be used for the power and ground planes and some other low density signals, while the "aggressive" rule circuit would be used for the signal interconnects. This approach also requires that there not be many interconnections between the two different rule circuits, which is probably the case for BTeV. We interconnect efficiently from circuit to circuit, using wire bonds. Furthermore, this approach, using two different design rule circuits, lends itself to an important performance improvement, namely mass reduction. Also it may be possible to find some vendor willing to

manufacture "standard" rule flex circuit with aluminum conductors, since aluminum is a lower Z material than copper and therefore causes much less scattering.

#### 2.2.2 Operation of the MCM

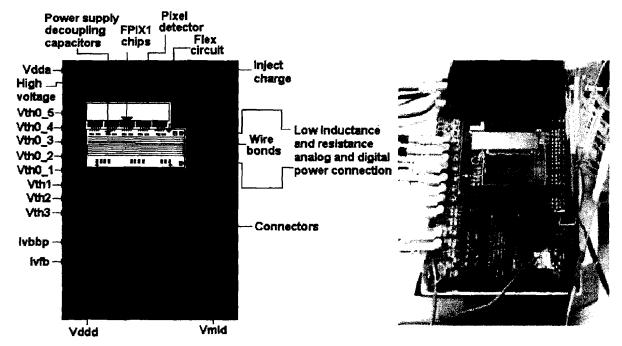

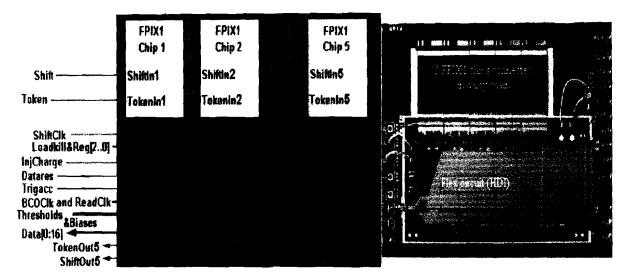

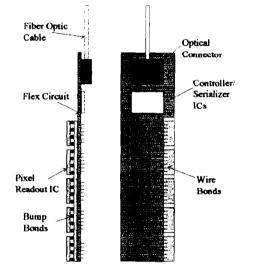

The Multi Chip Module (MCM) is the first attempt to characterize the performance of more than one chip bump bonded to a pixel detector. The MCM contains 5 FPIX1 chips connected in daisy chain. These are mounted on the top of a printed circuit board (PCB) designed for these test. A very high density circuit is required for signals interconnects in multiple FPIX1 chip designs. Limits on manufacturing prevent the use of conventional printed circuit boards (PCBs) to achieve the required high density. The FPIX1 chip bonding pads and signal traces on the prototype are on a multiple layer flex circuit manufactured by Fujitsu Computer Packaging Technologies Inc. Both the FPIX1's and the flex circuit are attached to the top of the PCB with the wire bonds going from the FPIX1 chips to the bonding pads on the flex cable. Figure 2.13 shows a sketch of the MCM assembled on the top of the PCB.

Several decoupling capacitors are mounted on the flex circuit. Power and ground are connected through heavy low resistance and inductance connections (i.e. posts interconnecting the flex circuit with the PCB). The power supply decoupling capacitors need to be located close to the pixel chips. Most of the signals are bussed in parallel to all chips with the exception of ShiftIn, ShiftOut, TokenIn and TokenOut that are daisy chained. Two bias current needs to be provided to the FPIX1 chip Ivbbp and Ivfb. Other bias currents are used for decoupling and optimization.

Figure 2.13. Sketch of the Fermilab Pixel Module.

All the bias currents are of the same type and are tied together (one trace feeding all FPIX1 chips for each bias current). They are accessible to the rigid board through the wire bonds. The rigid board of the MCM contains resistors to allow the setting of all bias currents. Each of the four

threshold voltages, Vth0, Vth1, Vth2, and Vth3, are also be tied together through the connector. The thresholds need also to be decoupled by capacitors mounted on the top of the flex circuit. There will be 324 microns between the centers of the outside pads of two adjoining FPIX1 chips. Figure 2.14 shows a block diagram of the flex circuit and a photograph.

Figure 2.14. Block diagram of the flex circuit and a photograph.

Fujitsu Computer Packaging Technologies (FCPT) fabricated the flex circuit [8]. Because there are only 79.2 microns between pads a high density routing design is required in order to be able to route a trace between the outer row of pads of the FPIX1 chip. Minimum trace widths are 20 microns with a minimum clearance of 20 microns. Vias are also be very small. In table 4 we are shown Fujitsu's design rules.

| Via Hole Diameter               | 25 µm           |

|---------------------------------|-----------------|

| Via Cover Pad Diameter          | 108 µm          |

| Via Center Spacing              | 208 µm          |

| Via Cover Pad to Line Clearance | 20 µm           |

| Line Width                      | 20 µm           |

| Line to Line Clearance          | 20 µm           |

| Line Center Spacing             | <i>m ب</i> 40 A |

Table 4 FCTP's design rules.

The two rows of pads on the FPIX1 chip require a very high density design. The vias must be very small in order to fit between the traces. The traces need to be very small in order to permit the vias to be placed. A bus of top layer traces runs horizontally from the bonding pads that connect the flex circuit to the PCB. This bus of traces connects all of the common signals to the five FPIX1 chips. The second layer has traces that connect the FPIX1 chip signals to the bus. The trace widths are 20 microns with a  $20 \,\mu m$  clearance. Vias will be 108 microns with a 25 micron hole size. Layer 3 is a power plane for Vddd and Vdda. Layer 4 is the ground plane. The MCM operates like a single FPIX1, with the only difference that in the single FPIX1 we only had 2880 pixel cells, and with the MCM we have 14400 pixel cells. In the single FPIX1 we found that the **ShiftOut** signal is inverted in relation of **ShiftIn**. This presented a problem when we connected them in a daisy chain. To solve the problem we designed the mask in a special way to download information to the chips both for initialization and to select the cells to be characterized. The readout operates more or less like a single FPIX1. The only difference is in the **TokenIn** signal. You need to be careful setting this signal because if you don't keep this signal at logic high for a sufficient time to readout all five chips, you can lose all the information.

#### 2.2.3 Design of patterns to control the MCM

We need to design the patterns in order to download the information to control the chip and to read out the information generated by an injection on a specific pixel cell to characterize it. Since in the MCM we have 5 chips connected in daisy chain, and the ShiftOut signal is inverted respect to ShiftIn signal we need to send the mask in a specific format to avoid this problem. When you have only one chip on the module there is no problem, but when you add another chip, then you will have this problem, and to avoid it we decide to invert the logic of the commands, i.e. where you were sending a logic one to the first chip you need to send a logic zero to the second and vice verse. So we noticed that if we program an even number of chips we need to send the first mask in negative logic, and if we program an odd number of chips we need to send the first mask in positive logic. We synthesize this explanation in Table 3.

| Number of FPIX1 chips | Logic of the mask |

|-----------------------|-------------------|

| 1                     | + .               |

| 2                     | -+                |

| 3                     | + - +             |

| 4                     | -+-+              |

| 5                     | + - + - +         |

| Table 3. Format to send the masks in the MCM | Table 3. | Format | to send | the masks | in the | MCM |

|----------------------------------------------|----------|--------|---------|-----------|--------|-----|

|----------------------------------------------|----------|--------|---------|-----------|--------|-----|

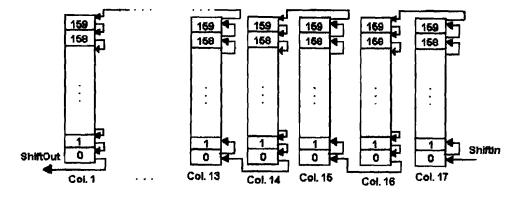

The first set of information that we download to the chip is in an array of commands called initialization. This array contains all the commands to do a reset and the configuration. To do a reset we need to send the scan path code 011 (**Reg2=0**, **Reg1=1**, **Reg0=1**) and 102 bits of zero logic by means of the ShiftIn pad, sending also the clock signal by the pad ShiftClk. Afterwards, we configure the FPIX1 chip. So, we select the scan path code 101 (**Reg2=1**, **Reg1=0**, **Reg0=1**). In this mask we send the lag number equal to two, to fill the 6 BCO bits, the chip ID number using the 4 ChipID bits, and, the mode of operation that is 1 bit long. This means that the mask is 11X5 bits long. A sketch of the FPIX1 chip initialization is shown in fig.2.15.

Figure 2.15 Initialization mask for the MCM

Later on we need to send the kill/inject mask selected by means of the path 111 (**Reg2**=1, **Reg1**=1, **Reg0**=1) or 110, which one we are selecting the pixel or pixel cells to be characterize. The kill mask is 14400 (2880x5) bits long, the inject mask is 14400 bits long. These bits correspond the 14400 pixel cells that the MCM contains. The format that we utilize to send these bits is as follows: the first 2880 bits are in positive logic, i.e., we send a zero logic in the kill mask to indicate that the specific pixel cell should be enabled to receive charge on it. Meanwhile we send logic one to indicate that a pixel cell should be disable. In the inject mask a logic one indicates that the pixel cell will not be injected and a logic zero that it will be. The second 2880 bits are in negative logic, that is the inverse logic of the first 2880 bits; the third are in positive logic; the fourth are in negative logic; and the fifth are in positive logic. The **ShiftIn** is delayed one pulse of clock from the **ShiftClk**. The frequency of the shift-clock is 12.5MHz. The **loadKill** needs to be enabled during the kill mask and disabled for the inject mask. In figure 2.16 we show the kill/inject mask for the MCM.

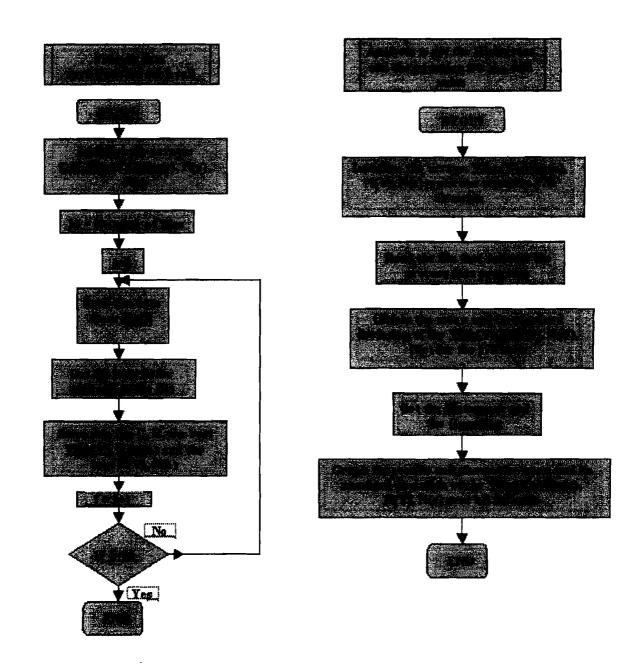

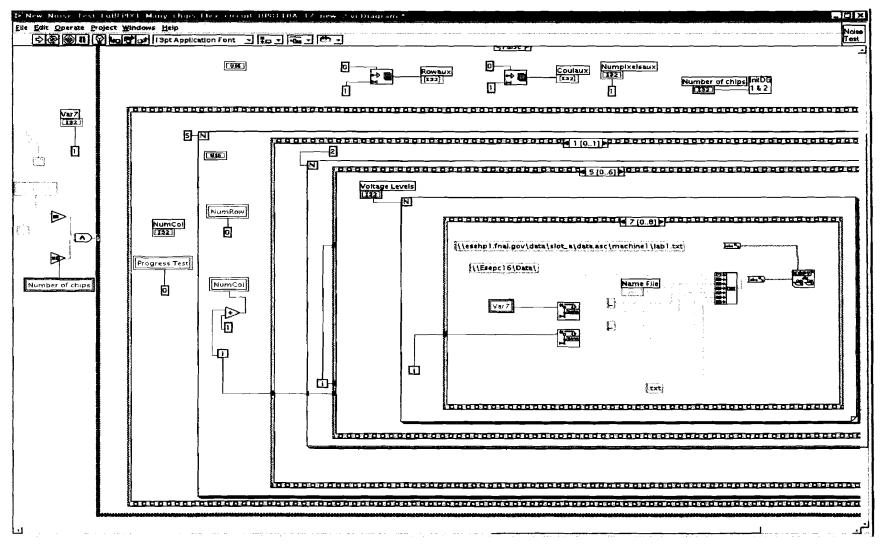

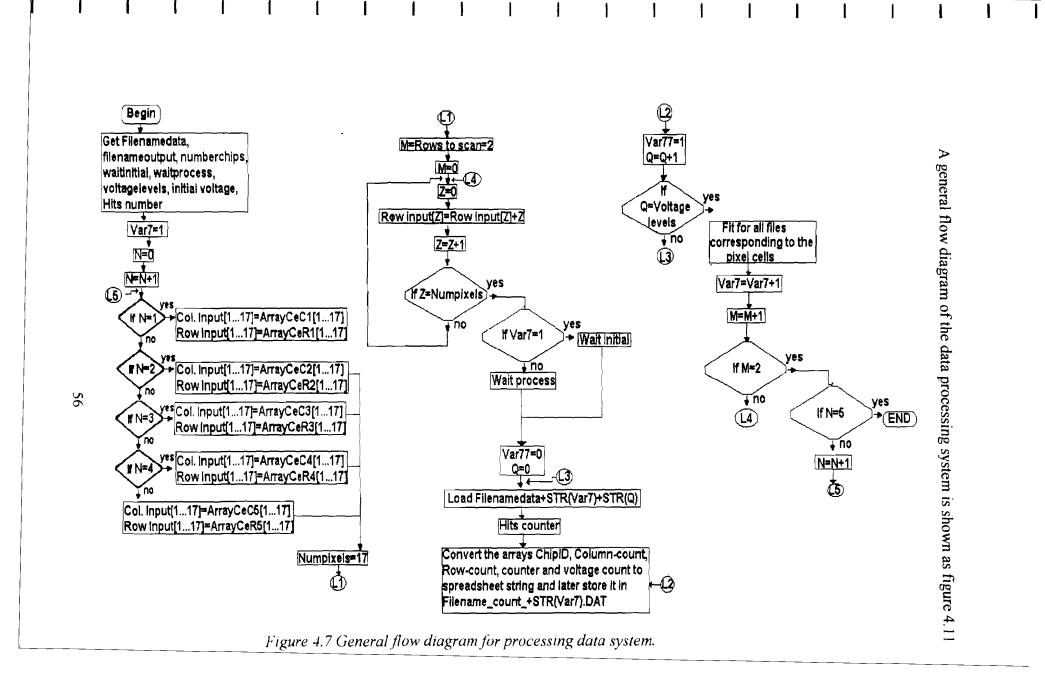

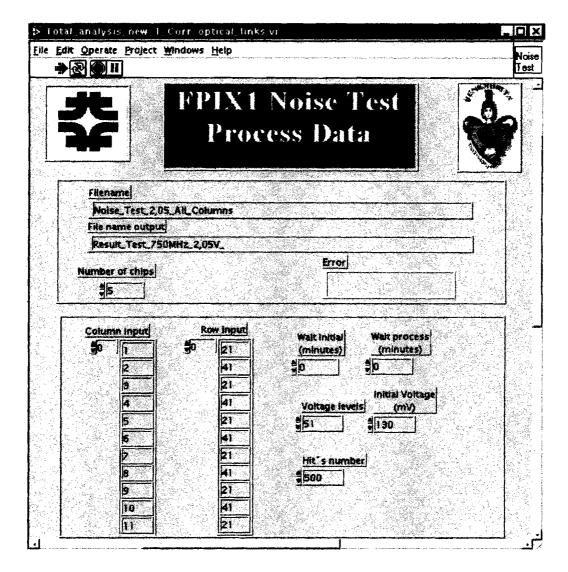

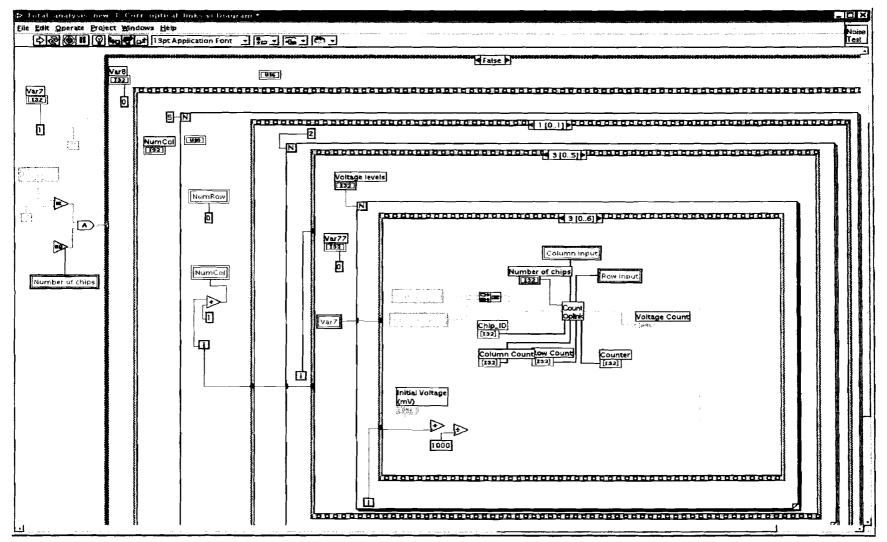

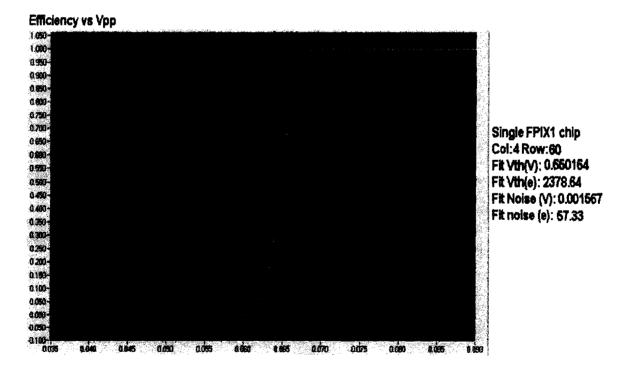

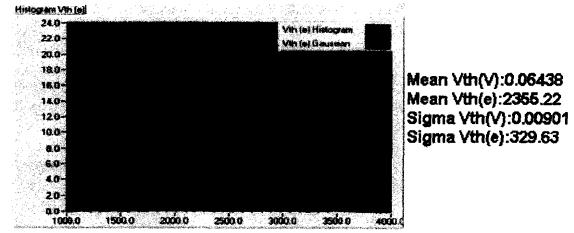

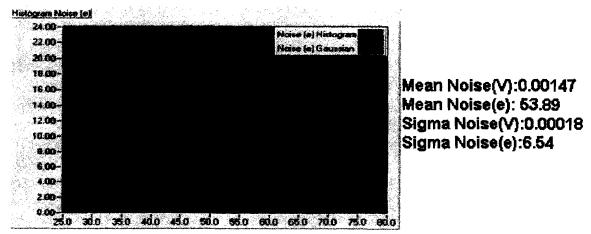

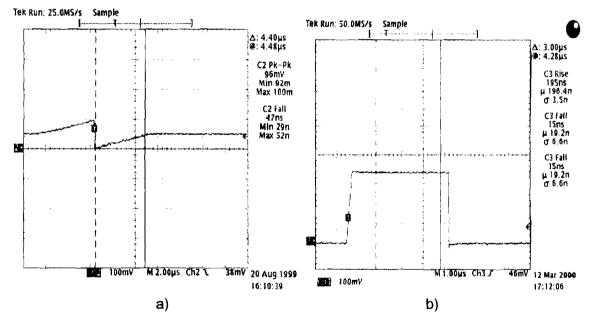

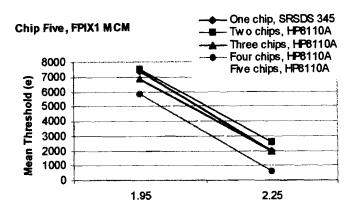

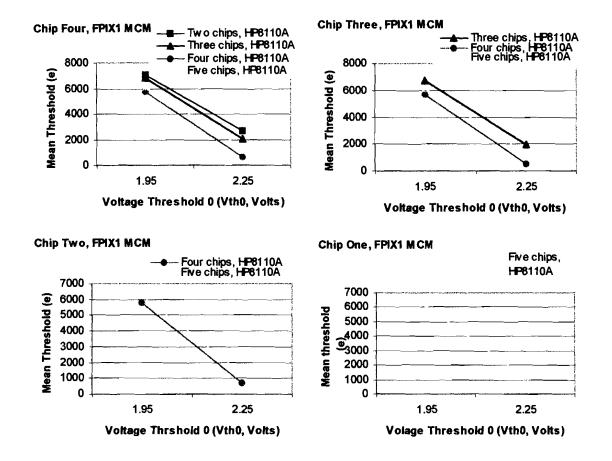

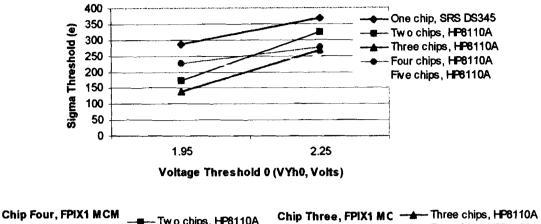

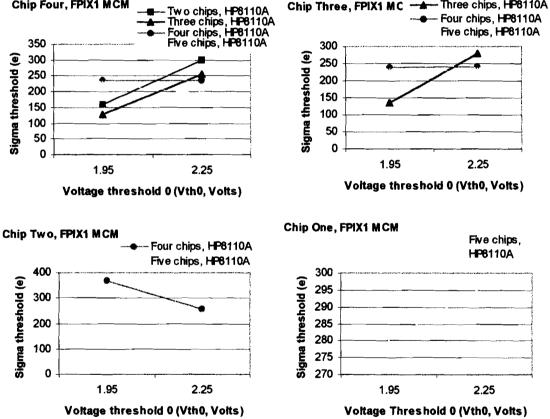

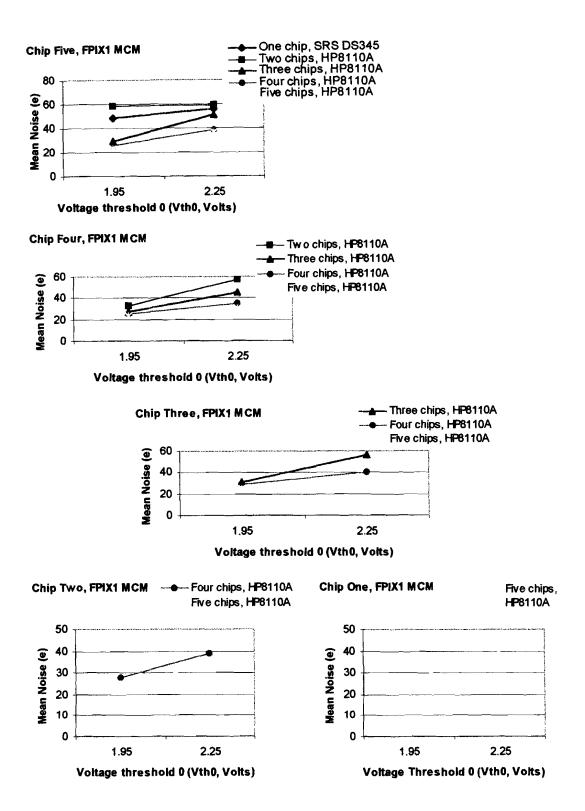

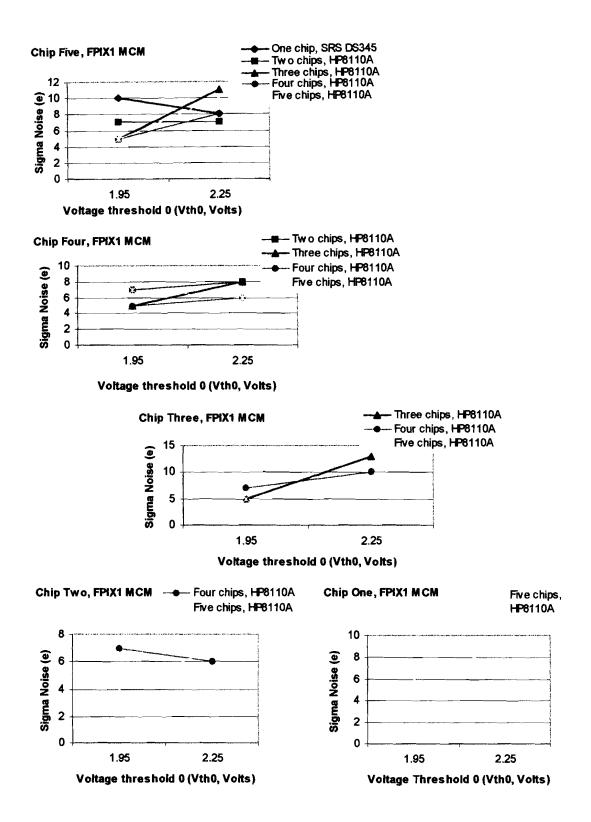

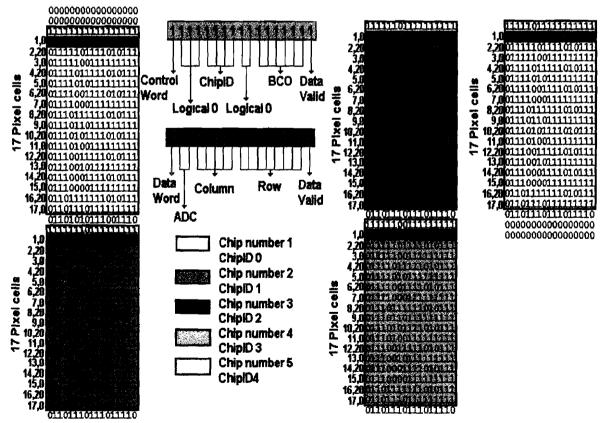

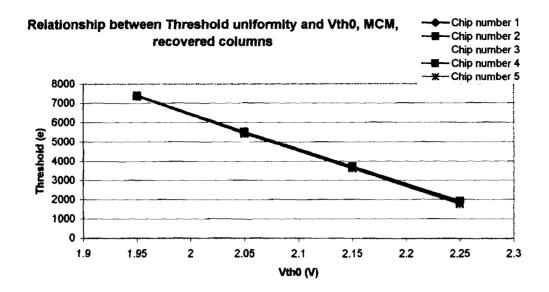

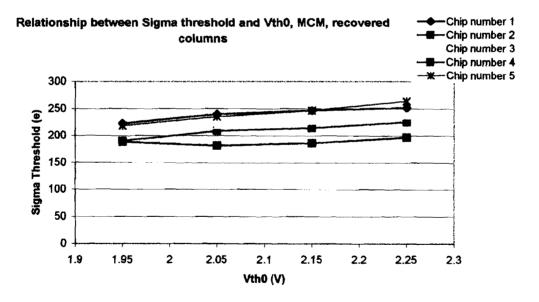

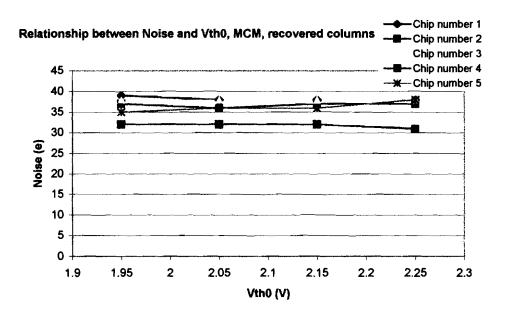

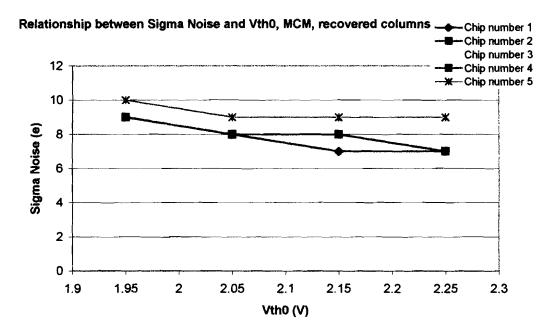

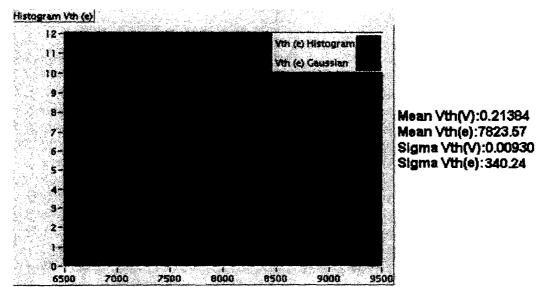

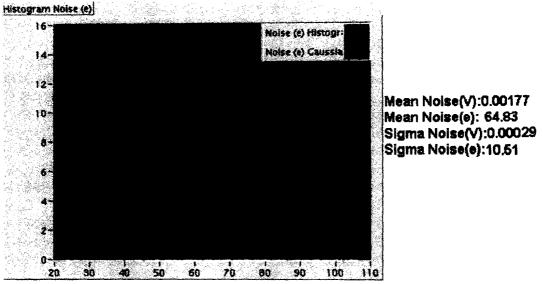

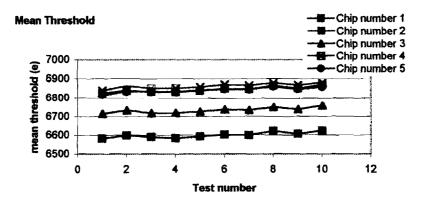

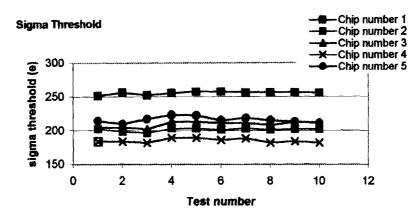

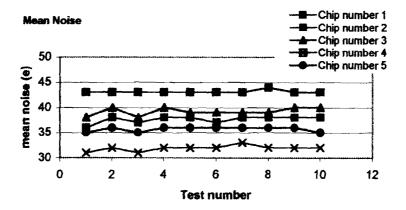

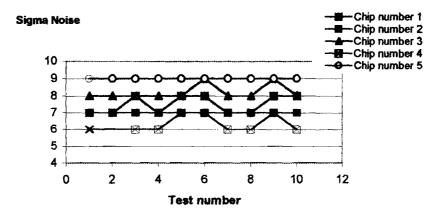

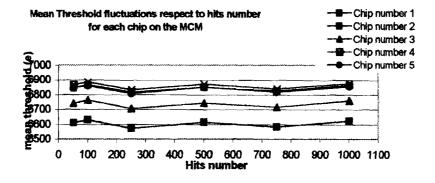

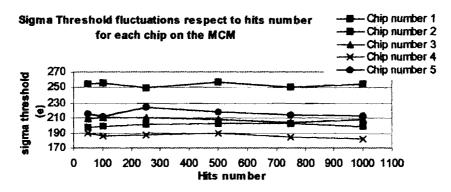

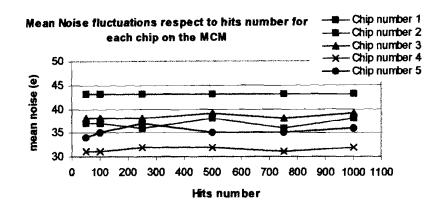

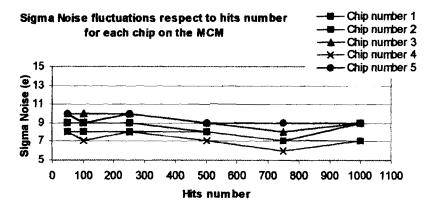

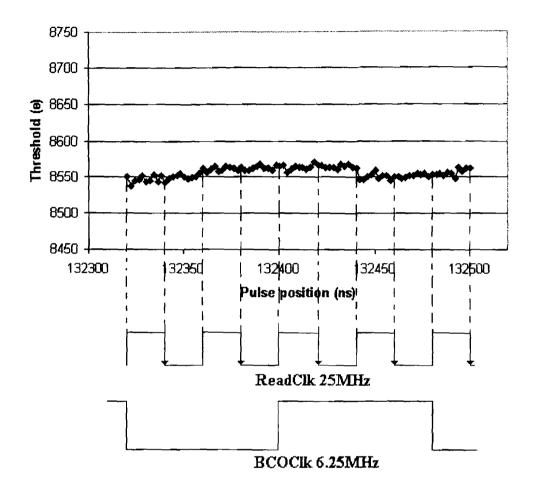

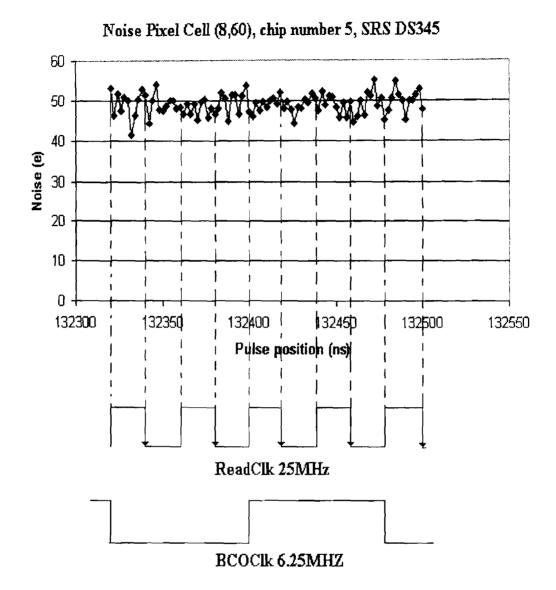

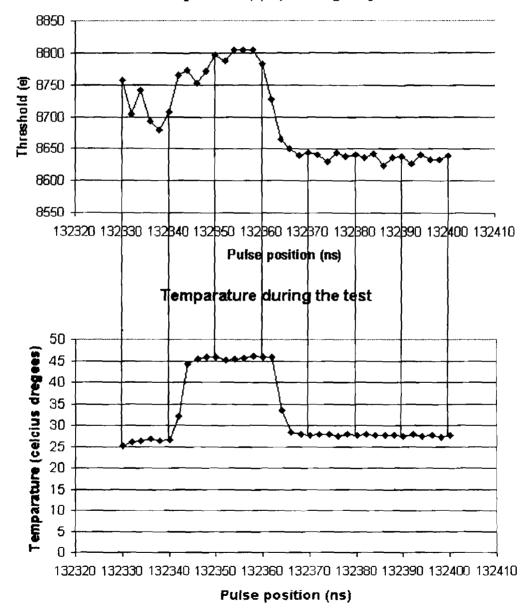

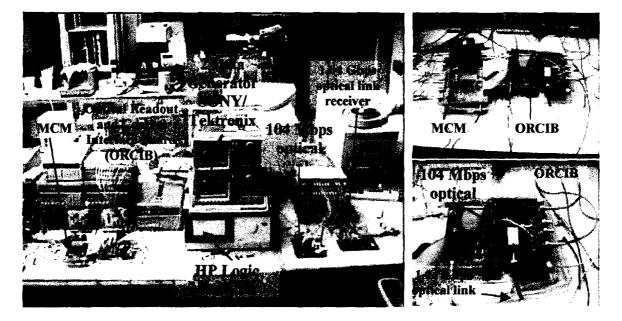

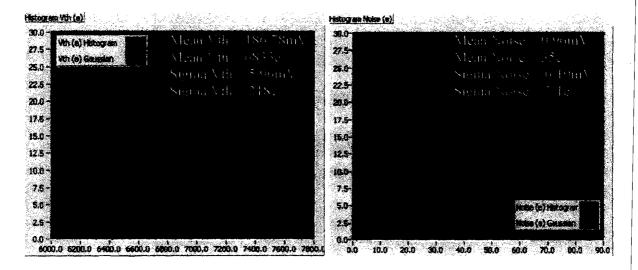

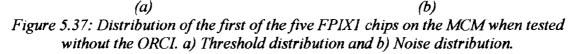

Figure 2.16 Kill/inject mask for the MCM.