A FASTBUS LOGIC STATE ANALYZER

ВҮ

#### SERGIO ZIMMERMANN

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the School of Advanced Studies of Illinois Intitute of Technology

Approved\_\_\_\_ Advis

Chicago, Illinois December, 1985

#### ACKNOWLEDGMENT

To make this thesis possible many persons and institutions from U.S.A. and Brazil contributed both, directly and indirectly.

From U.S.A. the Author wishes to thank Dr. George D. Kraft, his adviser from IIT, for his support and help in this thesis. He wishes to thank Edward Barsotti, leader of the Data System Group of CDF from Fermilab, for chosing him to develop this work and supporting its development. He wishes to thank Willian Graves for helping him to correct the manuscripts, Rudy Vabalaitis for doing the figures and Joel Zautner for helping him to test the hardware and software of the Snoop Modules. All these gentlemen are from the Data System Group of CDF of Fermilab. He wishes to thank Jeffrey Marsh from the Software Group of CDF of Fermilab for explaining him features of the VAX/VMS Operating System. He wishes to thank Dr. Leon Lederman and Dr. Roy Rubinstein from Fermilab, for proposing and organizing this joint colaboration Fermilab-Brazil. He wishes to thank the designers of the Snoop Module, Helmut V. Waltz and David B. Gustavson, from the Stanford Linear Accelerator Center, for providing the two Snoop Modules and associated valuable information.

From Brazil, the Author wishes to thank his colleagues of the Electronic Division of the Instituto de Fisica da UFRGS, Miguel Fachin Jr., Mauro Wyrsykoski, Mauro Fin, Arthur Boss Jr., Agostinho Bulla, Celso Muller and Paulo Pedro Petry for handling the extra load of work while he was absent. He wishes to thank Dr. Fernando Zawislak, Dr. Bernardo Liberman, Dr. Edemundo do Rocha Vieira and Dr. James Viccaro from the Instituto de Fisica da UFRGS for giving him valuable support and conditions for his absence for two years from his duties at that institution. He wishes to thank Miguel Fachin Jr., Aderbal Fernandes Lima and Marco Bittencourt from Equipamentos Cientificos e Industriais Ltda. for handling the extra load of work. He wishes to thank the Conselho Nacional de Desenvolvimento Cientifico e Tecnologico for the financial support.

The Author wishes to thank his wife, Marise, his parents, Bruno and Emma, and his brother and sister-in-law Paulo and Cristina, and a friend, Carlos Gary Faria for all the help and support.

S. Z.

iii

.

# TABLE OF CONTENTS

| ACKNOWLE      |                                                                                      | Page<br>iii |

|---------------|--------------------------------------------------------------------------------------|-------------|

| LIST OF       | TABLES                                                                               | vi          |

| LIST OF       | FIGURES                                                                              | vii ·       |

| CHAPTER<br>I. | INTRODUCTION                                                                         | 1           |

| II.           | MONITORING FASTBUS IN THE DATA AQUISITION<br>SYSTEM                                  | 6           |

|               | Error Detection And Reporting Specified By<br>The FASTBUS Standard                   | 6           |

|               | Point Boards                                                                         | 8<br>1 0    |

| III.          |                                                                                      | 11          |

|               | Hardware Modifications Regarding The<br>Arbitration Cycle                            | 11          |

|               | Hardware Modifications To Record FASTBUS<br>AS, AK, DS And DK Lines                  | 14          |

|               | Test Capabilities                                                                    | 14          |

| IV.           | The Silo Memory                                                                      | 14<br>17    |

|               | The Snoop Module Interfaced To A Terminal .<br>The Snoop Module Interfaced To A Host | 17          |

|               | Computer                                                                             | 25          |

| V.            | FUTURE DEVELOPMENTS                                                                  | 46          |

| VI.           | CONCLUSIONS                                                                          | 48          |

| APPENDIX      | \$                                                                                   |             |

| Α.            | FASTBUS DESCRIPTON                                                                   | 49          |

| В.            | SNOOP MODULE DESCRIPTION                                                             | 64          |

| с.            | SNOOP MODULE SOFTWARE                                                                | 74          |

.

.

|              |   |   |   |   |   |   |   |   |   |   |   |   | • |   |   |   |   |   |   |   |   | Page |

|--------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|

| BIBLIOGRAPHY | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | ٠ | • | ø | • | 0    |

r

V

# LIST OF TABLES

| Table<br>1. | Slave Data Time SS Responses                  | Page<br>7 |

|-------------|-----------------------------------------------|-----------|

| 2.          | Partial CSR-2 Bit Assigments                  | 8         |

| 3.          | FASTBUS Signals                               | 55        |

| 4.          | FASTBUS Signals Recorded in the Silo Memory . | 70        |

## LIST OF FIGURES

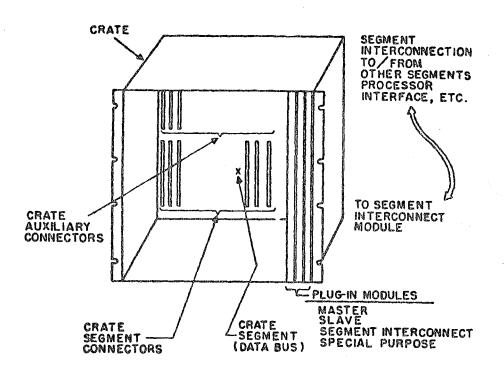

| Figure<br>1. | Basic FASTBUS Elements                                                               | Page<br>2 |

|--------------|--------------------------------------------------------------------------------------|-----------|

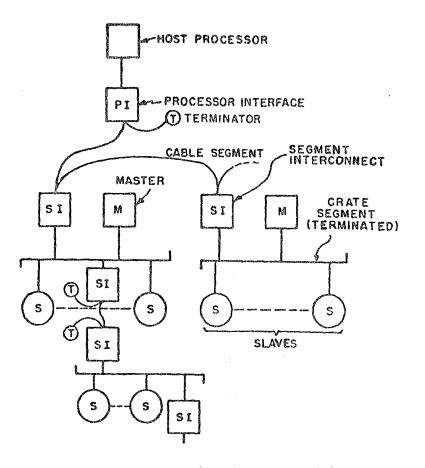

| 2.           | Examples of FASTBUS System Topology                                                  | 3         |

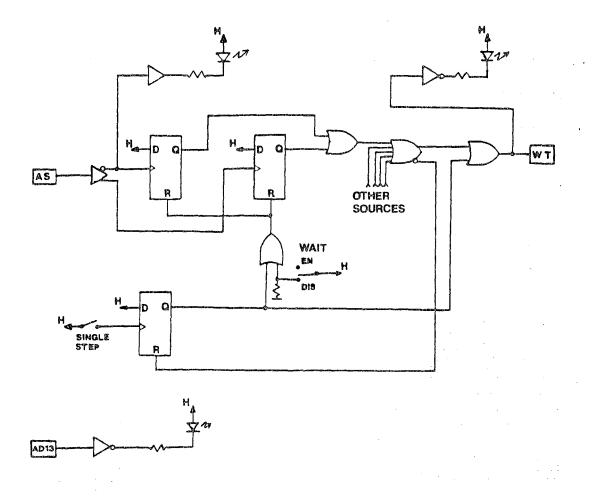

| 3.           | Basic Circuit of FASTBUS Displays Modules                                            | 9.        |

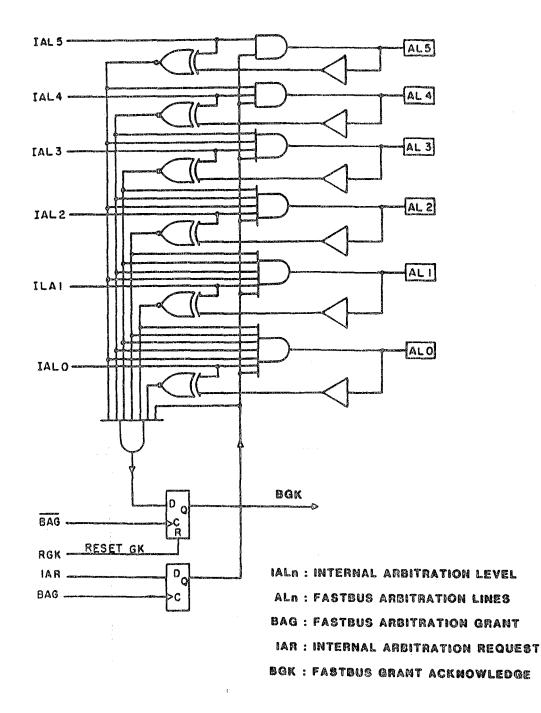

| Ц.           | Original Arbitration Circuitry in the Snoop<br>Module                                | 12        |

| 5.           | Changes Implemented in the Arbitration<br>Circuitry                                  | 13        |

| 6.           | Original Circuit of the Input/Output Buffers<br>Connected to FASTBUS AD and MS lines | 15        |

| 7.           | Changes Implemented to Enable Tests with the Silo Memory                             | 15        |

| 8.           | The Snoop Module Interfaced to a Terminal and<br>Connected to one FASTBUS Segment    | 18        |

| 9.           | Operation of the Snoop Module Connected to a<br>Terminal                             | 24        |

| 10.          | Example of Forth Words Written to Control the<br>Trigger Position                    | 25        |

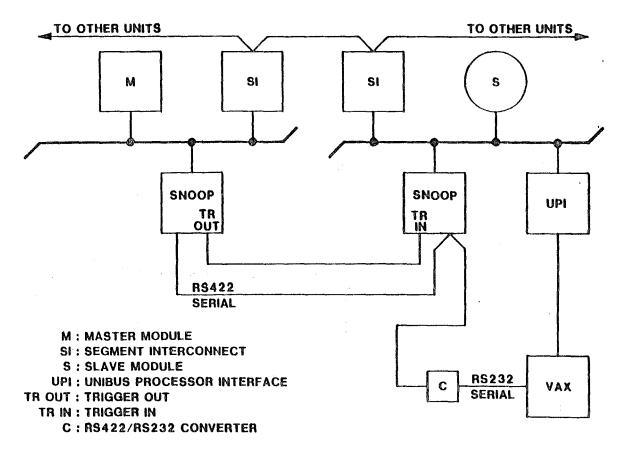

| 11.          | The Snoop Module Interfaced to a Host and<br>Connected to a FASTBUS System           | 27        |

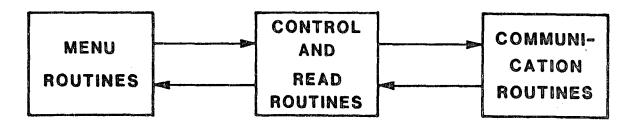

| 12.          | Interactions Among the Groups of Routines                                            | 28        |

| 13.          | Main Menu                                                                            | 29        |

| 14.          | First Page of the Setup for Recording Menu                                           | 30        |

| 15.          | Second Page of the Setup for Recording Menu .                                        | 30        |

| 16.          | Trap Words Menu                                                                      | 31        |

| 17.          | Analysis of the FASTBUS Transactions Recorded<br>Menu                                | 31        |

| 18.          | Stop Recording Menu                                                                  | 32        |

| 19.          | Example of a Host Computer Function Subprogram to Setup the Snoop Module             | 36        |

•

|               | •                                              |      |

|---------------|------------------------------------------------|------|

| Figure<br>20. | Examples of Forth Words Used by the Host to    | Page |

| 20.           | Control and Read the Snoop Modules             | 37   |

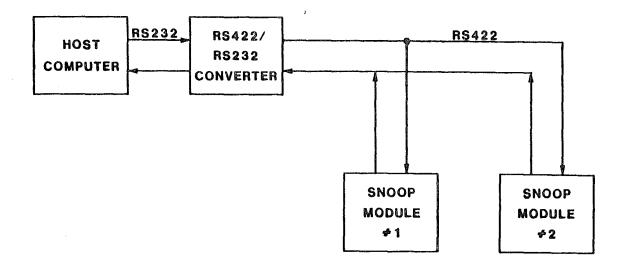

| 21.           | The Serial Interconnection of the Host and the |      |

|               | Snoop Modules                                  | 38   |

| 22.           | Typical Data Link Message Traffic              | 42   |

| 23.           | Data Link with a NAK                           | 43   |

| 24.           | Data Link with the Occurrence of Timeout       | 43   |

| 25.           | Part of the Communication Functions for the    | ·    |

|               | VAX                                            | 45   |

| 26.           | Example of FASTBUS Transaction Expressed in    |      |

|               | Disassembled Form                              | 47   |

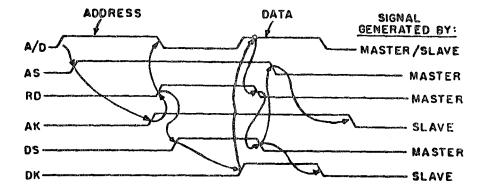

| 27.           | Basic Handshake Read Operation (As Seen by     |      |

|               | Master)                                        | 56   |

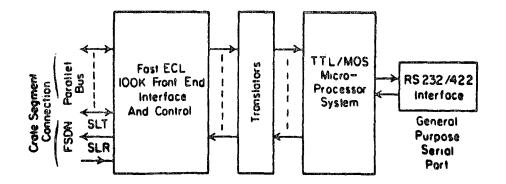

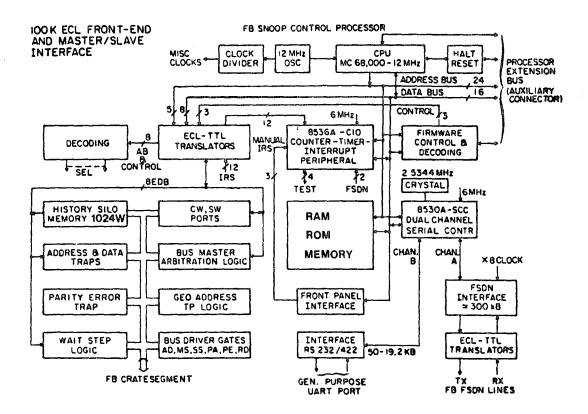

| 28.           | Snoop Module Organization                      | 66   |

| 29.           | Snoop Module Block Diagram                     | 67   |

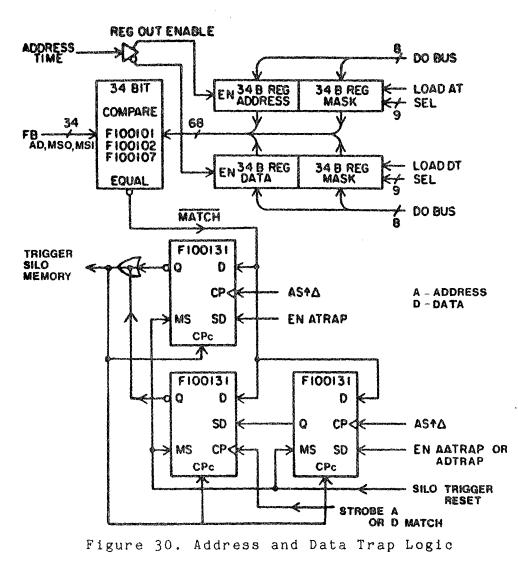

| 30.           | Address and Data Trap Logic                    | 68   |

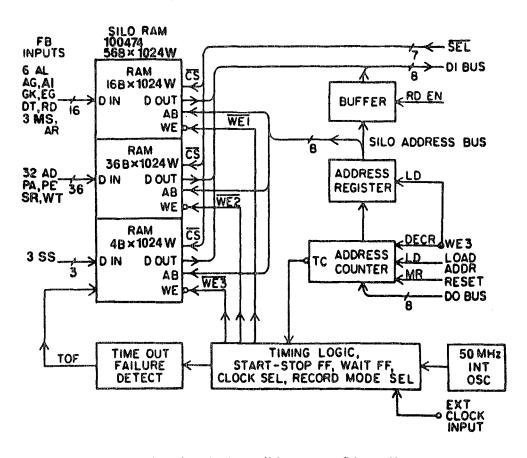

| 31.           | Activity History Silo Memory                   | 69   |

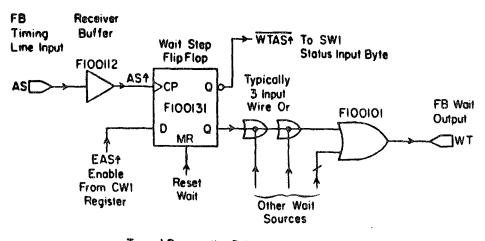

| 32.           | Typical Wait-Step Logic                        | 71   |

viii

•

ę.

# CHAPTER I INTRODUCTION

FASTBUS (1)\* is a standardized modular data-bus system for data aquisition, data processing and control. A FASTBUS system consists of multiple bus segments which can operate independently or be linked together with Segment Interconnects (see Appendix A) for passing data and other information.

At Fermi National Accelerator Laboratory (Fermilab), a data acquisition system for the Collider Detector Facility (CDF) based on FASTBUS is being developed. It will use about 60 FASTBUS Segments interconnected. Some form of diagnostic system, a kind of FASTBUS Logic State Analyzer, will be necessary to help to find, in real time, software and hardware faults occurring on the bus of this system.

The faults that are expected to happen on FASTBUS will range from very simple faults, like a constant absence of a signal on one FASTBUS line, to very complex faults, such as an error created by a faulty interaction among different FASTBUS Masters.

What tool(s) should be developed to expose these problems? There are currently no adequate tools (software or hardware) for examining improper behavior on FASTBUS. At this moment it is possible to foresee that a system that could record FASTBUS transactions into a silo memory (see

<sup>\*</sup>Numbers in parentheses refer to numbered references in the bibliography.

Appendix B) for later analysis, would be very helpful. The silo memory should be able to record activity on, at least, the most important FASTBUS lines.

The electric connections among FASTBUS modules are made of signal called a Segment. ЪУ set lines The usual а situation is that the required functionality at а given by a number of Modules being grouped location is attained together in a Crate in order to share a common backplane bus (see Fig. 1).

Figure 1. Basic FASTBUS Elements

Multiple Masters on a single Segment share common а bus. Contention for use of common а bus mav reduce throughput, as seen by a given Master, because of the time the Master spends waiting to gain Mastership. Since Segments operate independently, distributing the Masters

. 2

among several Segments can reduce the contention problem. Even so, a Master on one Segment must be able to quickly communicate with a slave on another Segment. This ability is provided by Segment Interconnects (SIs) which temporarily link independent segments (see Fig. 2).

Figure 2. Example of FASTBUS System Topology

A system with this characteristic should have the following facilities:

The recording of FASTBUS cycles should be done in one segment or in different segments at the same time, depending upon the needs of the system.

- It should have trigger capabilities to select only the FASTBUS cycles of interest.

- 3. It should be able to present to the user the cycles recorded in a comprehensive manner.

- 4. It should be easy to operate.

- 5. It should be able to analyze FASTBUS transactions and minimally interfere with the FASTBUS operations.

The Snoop Module (see Appendix B) was developed at the Stanford Linear Accelerator Center. It was used to develop this FASTBUS diagnostic system. The Snoop Module consists of a high-speed emitter-coupled logic (ECL) front-end, with monitoring and test capabilities, controlled by а Some modifications in the hardware of the microprocessor. Snoop Module were done in order to implement the characteristics required by this diagnostic system.

The following steps were done to implement the FASTBUS Analysis System using Snoop Modules:

- 1. Fully test and debug the Snoop Module.

- 2. Implement a set of FASTBUS monitoring tests that take full advantage of the flexibility of the Snoop module and are useful to trace FASTBUS problems.

- 3. Implement specific modifications to the basic circuitry of the Snoop Module.

- 4. Develop software tools that enable the user, in an easy way, to set the FASTBUS monitoring tests.

ц

- 5. Network the Snoop Modules in a multi-segment configuration and test their ability to trace FASTBUS problems.

- Test the ability of this diagnostic system to monitor FASTBUS transactions in different configurations.

#### CHAPTER II

#### MONITORING FASTBUS IN THE DATA ACQUISITION SYSTEM

FASTBUS is a very new standard which has never been used in an application of this size before. Consequently, there is no clear understanding of the types of problems that will occur during operation of the system.

To identify and trace such problems, several different forms of monitoring the bus have been implemented. In the next sections, a description of the FASTBUS monitoring capabilities is given and in what specific situations these capabilities are used.

# Error Detection and Reporting Specified by the FASTBUS Standard

The FASTBUS standard specifies mandatory and optional error detection and reporting techniques. The FASTBUS Slave Status Responses are one example of mandatory error The Slave Status Responses are detection and reporting. encoded on the FASTBUS SS lines and are sent to a Master by Slave or Segment Interconnect, along with the appropriate а FASTBUS acknowledgement. These responses are used by the Masters to determine their next course of action. Two sets of Slave Status Responses are defined for FASTBUS: one for Cycles Address and another for Data Cycles. The Slave Status Responses for a Data Cycle are shown Table 1. in These responses can be used by the Master to report the type of error found and can help the service person in tracing the fault.

| SS<2:0> | Interpretation           |

|---------|--------------------------|

| 0       | Valid Action             |

| 1       | Busy                     |

| 2       | End of Block             |

| 3       | User Defined             |

| 4       | Reserved                 |

| 5       | Reserved                 |

| 6       | Data Error - Data Reject |

| 7       | Data Error - Data Accept |

Table 1. Slave Data Time SS Responses

The FASTBUS standard also specifies some optional error detection mechanisms which report the occurrence of errors using bits in a Control and Status Register (CSR). For example, Table 2 shows bits 8 through 13 of CSR-2 and their significance when a FASTBUS Master reads these bits. A user of a FASTBUS system can read these bits as an aid in determining the cause of the errors which may occur.

Finally, the FASTBUS standard provides a set of user defined error detection and reporting techniques for FASTBUS module designers. See, for example, response SS=3 on Table 1.

| Bit | Significance for a read performed |

|-----|-----------------------------------|

|     | by a FASTBUS Master.              |

| 08  | Non-existing Address              |

| 09  | Device Data Overflow              |

| 10  | Word Count Overflow               |

| 11  | Device Full                       |

| 12  | Device Not Empty                  |

| 13  | Inputs Not Present                |

Table 2. Partial CSR 2 Bit Assignments

## Monitoring Using Display Modules and Test Point Boards

Display Modules (2) are FASTBUS modules which show the logical level of each FASTBUS line. This is accomplished by means of buffers which drive light emitting diodes (LEDs) on the front panel of the module (see Fig. 3). They also have internal circuitry which allows the user to assert the FASTBUS Wait line each time a transition occurs on the AR, AG, AS, AK, DS or DK lines. This provides a means to perform single step operations on FASTBUS.

Test Point boards are boards with the same dimensions as a FASTBUS module. Through a connector, each FASTBUS line is accessible and is interfaced by a buffer to the front panel of the board. The state of all FASTBUS lines can be examined using this board and an oscilloscope.

Figure 3. Basic Circuit of FASTBUS Display Modules

The Display Modules and the Test Point boards are useful for the development of FASTBUS modules. However, they proved to be of little value for tracing faults on a huge FASTBUS system. For example, a FASTBUS multi-master system cannot normally be single stepped.

# <u>The Need for Another Form of Monitoring: The FASTBUS Logic</u> Analyzer

There are faults which occur on FASTBUS that can only be produced by the data acquisition system itself, or that may be simulated on test systems external to the data acquisition. A logic state analyzer is the main tool used to locate these faults.

However, logic state analyzers are not designed for monitoring FASTBUS. They have the following disadvantages when used to trace problems on FASTBUS:

- 1. It is difficult to connect them to a FASTBUS Segment.

- 2. It is difficult to configure them to record FASTBUS transactions in the most efficient way.

- 3. It is difficult to use them to trace data and control information going from Segment to Segment.

- 4. Logic state analyzers of good quality are expensive (approximately \$25,000).

Because of these disadvantages, the usage of Snoop Modules was implemented to monitor FASTBUS. The Snoop implementation is described in this thesis.

#### CHAPTER III

#### HARDWARE CHANGES AND TESTS IMPLEMENTED WITH

#### THE SNOOP MODULES

Some hardware changes had to be implemented on the Snoop Module board in order to provide certain modes of silo memory recording which were not available on the original board. More hardware changes were made to implement additional self test capabilities. Finally, the Snoop Module, itself, was subject to a variety of tests to establish how reliably it functioned.

#### Hardware Modifications Regarding the Arbitration Cycle

The original circuitry of the Snoop Module did not provide a means to detect specific Arbitration Cycles on the bus. This is an important condition to select which FASTBUS transactions must be recorded into the silo memory.

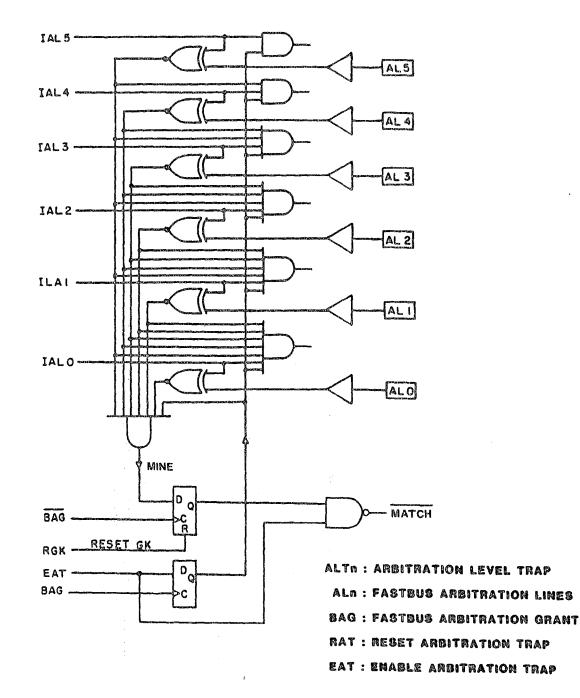

The Arbitration Logic circuit of the Snoop Module was modified in order to implement this feature. This circuit enables the Snoop Module to request mastership of the bus. Figure 4 shows the original circuit; and Figure 5 shows the circuity with the changes implemented.

The (XOR-NOT) gates are comparators which have their outputs set to one when both the Internal Arbitration Level and the Arbitration Level of the Master which granted bus mastership are equal.

Figure 4. Original Arbitration Circuitry in the Snoop Module

Figure 5. Changes Implemented in the Arbitration Circuitry

<u>Hardware Modifications to Record FASTBUS AS, AK, DS and DK</u> lines

When timing monitoring is being done on FASTBUS, it is imperative to record the FASTBUS timing lines (AS, AK, DS and DK) into the silo memory. This feature is necessary to enable the user to determine when the Address and Data Cycles have occurred. This facility was implemented by adding one more 1 K x 4 ECL randon access memory (RAM) to the silo memory.

#### Hardware Modifications to Increase Self Test Capabilities

Hardware changes were implemented to enable the user to test part of the front-end logic of the Snoop Module, independent of FASTBUS transactions.

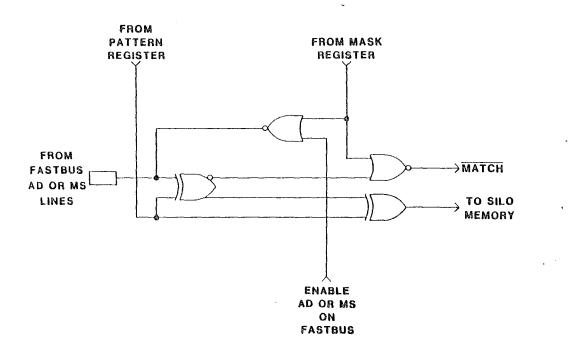

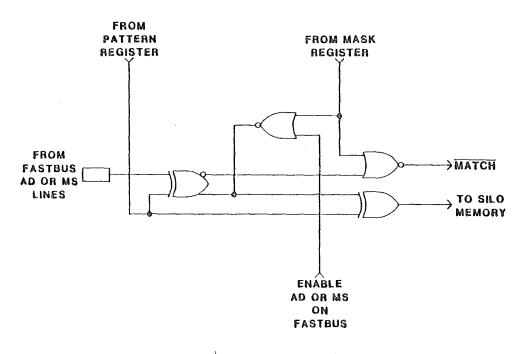

The output buffers which enable the Snoop Module to drive the FASTBUS lines (see Fig. 6) were modified as shown in Figure 7. With this new scheme, known test data may be recorded into the silo memory for later checking independent of the FASTBUS transactions.

## Test Recording FASTBUS Transactions Into The Silo Memory

Many tests were done with the Snoop Module in order to debug and test the board. One of the tests implemented was done to determine if the trigger and the recording into the silo memory were reliable operations.

Figure 6. Original Circuit of the Input/Output Buffers Connected to FASTBUS AD and MS Lines

Figure 7. Changes Implemented to Enable Tests with the Silo Memory

A Snoop Module was connected to a FASTBUS Segment where a Master was performing known FASTBUS cycles involving arbitration, address and data with two different Slaves. Two different triggers (see Appendix B) were used to start recording FASTBUS transactions into the silo memory. Thesetwo triggers were alternated and used to record different patterns of data in the silo memory. The silo memory was filled using one trigger and then checked for errors; afterwhich, the other trigger was used to refill the silo memory for further error checking. This error checking, which was performed by the control microprocessor of the Snoop Module, was repeated 24 hours a day for two weeks without a single error being detected.

#### CHAPTER IV

#### SOFTWARE FOR THE FASTBUS LOGIC STATE ANALYZER

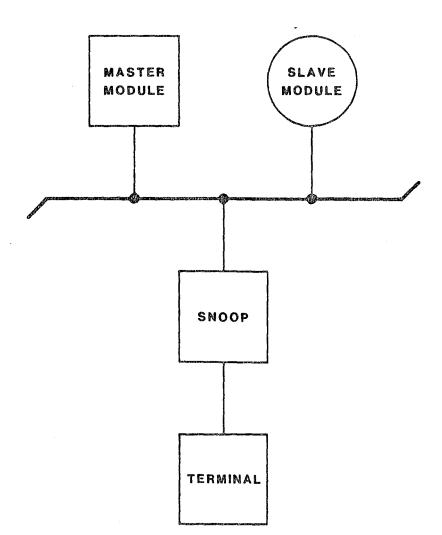

Two different operation modes have been developed for using the Snoop Modules: one consists of a terminal interfaced to a single Snoop Module residing in one Segment, and the other consists of a host computer connected to one or more Snoop Modules residing on different Segments. The following sections describe these two configurations and their associated software.

#### The Snoop Module Interfaced to a Terminal

Figure 8 shows a typical configuration of a Snoop Module monitoring a FASTBUS segment when interfaced to a terminal. This mode of operation is well suited for developing FASTBUS modules in a test system or for monitoring single segments of a data acquisition system. Its setup time is minimal and no connection to a host computer is needed.

An on-board microprocessor controls the front-end logic of the Snoop Module through a set of control and status registers (see Appendix B). The application software developed provides the user with a set of commands which enable him to control these registers and read the silo memory. This software was written in two different languages: Forth (3 and 4) and Assembler. Assembler was used in all speed critical points.

Figure 8. The Snoop Module Interfaced to a Terminal and Connected to One FASTBUS Segment

The commands, normally called words by Forth, allow the user to configure the Snoop Module to record FASTBUS transactions, to observe the different steps in the recording process, and to examine the silo memory. These words give the user complete control of the various monitoring capabilities of the Snoop Module (see Appendix C). These Forth words are listed below:

- Words to set the Arbitration, Address and Data Traps:

- a. <pattern (byte)> TP-L!: Set the AL trap for the Arbitration Trap.

- b. <pattern (double word)> <mask (double word)>

TP-A-AD!: Set the AD trap for the Address

Trap.

- c. <pattern (double word)> <mask (double word)>

TP-D-AD!: Set the AD trap for the Data or the

Second Address Trap.

- d. <mask (double word)> TP-A-AD-M!: Set the mask of the AD trap for the Address Trap.

- e. <pattern (double word)> TP-A-AD-P!: Set the pattern of the AD trap for the Address Trap.

- f. <mask (double word)> TP-D-AD-M!: Set the mask of the AD trap for the Data or Second Address Trap.

- g. <pattern (double word)> TP-D-AD-P!: Set the pattern of the AD trap for the Data or Second Address Trap.

- h. <pattern (byte)> <mask (byte)> TP-A-MS!: Set the MS trap for the Address Trap.

- i. <pattern (byte)> <mask (byte)> TP-D-MS!: Set the MS trap for the Data or the Second Address Trap.

- j. <mask (byte)> TP-A-MS-M!: Set the mask for the MS trap for the Address Trap.

- k. <pattern (byte)> TP-A-MS-P1: Set the pattern

for the MS trap for the Address Trap.

- 1. <mask (byte)> TP-D-MS-M!: Set the mask for the MS trap for the Data or Second Address Trap.

- m. <pattern (byte)> TP-D-MS-P!: Set the pattern for the MS trap for the Data or Second Address Trap.

- n. ?TP: Show all traps set to the trigger sequence chosen.

- o. ?TP-L: Get the setup of the AL trap for the Arbitration Trap.

- p. ?TP-A: Get the setup for the AD and MS trap for the Address Trap.

- q. ?TP-D: Get the setup for the AD and MS trap for the Data or the Second Address Trap.

- 2. Words to set different Trigger Sequences:

- a. TR-SEQ-LAD: Set arbitration, address and data cycle as trigger sequence.

- b. TR-SEQ-LAA: Set arbitration, address and another address cycle as trigger sequence.

- c. TR-SEQ-LA: Set arbitration and an address cycle as trigger sequence.

- d. TR-SEQ-AD: Set address and data cycle as trigger sequence.

- e. TR-SEQ-AA: Set address and a second address cycle as trigger sequence.

- f. TR-SEQ-A: Set address cycle as trigger sequence.

- 3. Words to set the Trigger Source:

- a. TR-SRC-I: Set the use of the internal trigger source.

- b. TR-SRC-E: Set the use of the external trigger source.

- c. TR-SRC-M: Set the use of the microprocessor to trigger. The trigger is asynchronous with FASTBUS transactions.

- 4. Words to set the Position of the Trigger among other transactions recorded:

- a. TR-POS-B: Set the trigger position to the beginning of cycles recorded.

- b. TR-POS-E: Set the trigger position to the end of cycles recorded.

- 5. Words to select the type of FASTBUS cycles to record:

- a. TY-REC-ALL: Set to record all types of cycles.

- TY-REC-NOD: Set to record all type except data cycles.

- 6. Words to select the type of sampling strobe:

- a. SS-SRC-FB: Set FASTBUS transactions as source for generation of sampling strobes.

- b. SS-SRC-IC: Set the internal 50 MHz clock as source for generation of sampling strobes.

- c. SS-SRC-EC: Set an external clock as source for generation of sampling strobes.

- 7. Words to read the setup of the fast front-end. logic:

- a. ?SET-REC: Show all the setup of the fast front-end logic for the recording of FASTBUS transactions into the silo memory.

- b. ?TR-SRC: Show the trigger source setup.

- c. ?TR-POS: Show the trigger position setup.

- d. ?TR-SEQ: Show the trigger sequency setup.

- e. ?TY-REC: Show the type of cycle to record setup.

- f. ?SS-SRC: Show the sampling strobe source setup.

- 8. Words to control the silo memory address counter:

- a. <silo address (word)> SIA!: Set the silo address counter.

- b. ?SIA: Read the silo address counter.

- c. SIA1+: Increment the silo address counter by 1.

- 9. Words to read the silo memory:

- <1st address (word)> <no. of cycles a. to list (word)> SILO: List all FASTBUS lines recorded in the silo memory, starting at 1st address, until the number of cycles to list is

completed.

- b. SILOC: Read all FASTBUS lines recorded in the silo memory in the address previous set in the silo memory address counter. After listing, decrement the address counter by one.

- c. LID: List the identification of each FASTBUS line shown by SILOC.

- 10. Words to control the execution of the recording process:

- a. START-REC: Record FASTBUS cycles.

- b. ?STATUS-REC: Read the status of the recording into the silo memory of the Snoop Module. It stays showing the status until <ESC> is pressed or the recording operation finishes.

- c. STOP-REC: Stop the recording into silo memory.

- d. REC: Start recording and show the status of the recording. Stop recording when <ESC> is pressed or when the recording process finishes.

Figure 9 gives a typical example of the interaction between the user and the Snoop Module in this mode of operation. Note that comments were added just for illustration and that "OK" is the prompt sent by Forth. Figure 10 shows the Forth words written to control the trigger position when the user is working with this mode of operation.

TR-SEQ-AD ΟK ;Set the trigger sequence: ;address and data cycles. TR-POS-B ОК ;Set trigger position. ?TR-POS ;Check trigger position set. TRIGGER POSITION: Start of FASTBUS cycles recorded 0K ?TP - A;Read the address trap ;previously set. ADDRESS TRAP: AD pattern: #00000018 AD mask: #00000000 MS pattern: #1 MS mask: #0 ОК REC ;Start the recording operation. TRIGGER WAS NOT FOUND ;Stop this process by typing the ;key <ESC>. ОК #17. TR-A-AD! ΟK ;Change the AD lines trap for ;address trap. REC ;Start again the recording ; operation. TRIGGER WAS FOUND ;Snoop front-end logic found ;the trigger sequence. CYCLES BEING RECORDED ;Record FASTBUS cycles into ;silo memory. IT IS NOT RECORDING ;Finishes automatically the ;recording. ΟK 0 5 SILO ;Examine some cycles recorded

SIAD AlagGKar AL EGrd PApe SRwt MSss TOdt A D 0000017 000 0 0 1 0 11 0 0 1 1 0 0 1 0 0 0 00000000 1 1 0 0 2 0 0 001 0 0 1 0 11 0 0 1 00A20000 0 1 0 0 002 0 0 1 0 11 0 1 0 0 0 1 003 0 0 1 0 0 0000018 0 0 0 0 0 0 0 11 1 1 004 0 0 1 0 11 0 0 00004000 0 1 0 0 2 0 0 1 12AC3280 005 0 0 1 0 11 0 0 1 1 0 0 0 0 0 1 ΟK

Figure 9. Operation' of the Snoop Module Connected to a Terminal

| : | CB-TR-BG/END* CCR41;                                                                                                          | ( Set trigger position in the)<br>( end of cycles recorded.)<br>( Do this resetting bit in)<br>( control register 4.) |

|---|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| : | CB-TR-BG/END* SCR4!;                                                                                                          | ( Set trigger position in the)<br>( begin of cycles recorded.)<br>( Do this setting bit in)<br>( control register 4.) |

| : | <pre>?TR-POS ." TRIGGER POSITION: " CW4@ CB-TR-BG/END* ANI IF ." Start of FASTBUS ELSE ." End of FASTBUS of THEN SPACE;</pre> | •                                                                                                                     |

Figure 10. Example of the Forth Words Written to Control the Trigger Position

#### The Snoop Module Interfaced to a Host Computer

The employment of a host computer to control the Snoop Module creates numerous interesting possibilities:

- a. The use of software utility packages resident in the host to develop the software of the Analysis System, like the menu oriented command interface, software graphics packages, etc.

- b. The use of the devices connected to the host like disks, graphic printers, etc.

- c. The use of the host computer to analyze the data recorded by the Snoop Modules. For example, if an error happens a few times every hour, a program can be developed for the host to automatically setup the Snoop Modules and check the transactions recorded.

d. The application software developed for the host computer is relatively independent of the Snoop Module hardware, decreasing the number of changes necessary in the software in case of hardware upgrading.

A VAX from Digital Equipment Corporation is used for the host computer in this system. These computers are also used to control the data acquisition system.

Figure 11 shows a possible configuration in which two Snoop Modules controlled by the host computer are monitoring a FASTBUS system. Note that the Unibus Processor Interface (5) is a FASTBUS module which interfaces the VAX and FASTBUS. One typical capability which this configuration provides is the recording of data and control information going from a Master located in one Segment to a Slave located in another. This can be accomplished in the the Snoop Module, closer to the Master, following way: is programmed to detect the trigger sequence of interest, and the other Snoop Module programmed to receive the trigger from the first. When the trigger sequence is detected by the Snoop Module closer to the Master, both modules start recording the bus activity at the same time. Once the recording process is finished, the user can call the host facilities to analyze the FASTBUS transactions.

The application software developed for this type of configuration can be divided into two groups: software resident in the host computer and software resident in the

Snoop Module. This software is described in the following sections. The communication between the host and the Snoop Modules is described at the end of this chapter.

Figure 11. The Snoop Module Interfaced to a Host and Connected to a FASTBUS System.

The Software Resident in the Host Computer: the application software developed for the host computer was written in FORTRAN (6).

This software has three different groups of routines:

- 1. Routines which enable the user to control the

- system and analyze the transactions recorded.

- 2. Routines to control the Snoop Module and read the silo memory.

- 3. Routines to perform the communication with the Snoop Modules.

The interaction among these groups is shown on Figure 12.

Figure 12. Interactions Among the Groups of Routines

A software package was developed at Fermi National Accelerator Laboratory which enables programs to obtain both the commands and the data for the FASTBUS logic analyzer by means of menus (7). This software package was used to implement the menus for the Analysis System. In total there are five different types of menus:

- 1. The main menu.

- 2. The Snoop Module setup menu.

- 3. The trap words setup menu.

- 4. The analysis of the recorded FASTBUS cycles menu.

- 5. The stop recording menu.

Figure 13 shows the main menu. This menu is activated when the FASTBUS logic analyzer software begins running. This menu allows the user to choose the operation which he whishes to execute. Note that just two of the options presented have been developed: options A and B. The other options will be part of future developments and are explained in Chapter V.

> FASTBUS LOGIC STATE ANALYZER MAIN MENU

A - Setup for the Recording of FASTBUS Transactions

B - Analysis of the FASTBUS Cycles Recorded

C - Setup for the assertions of the Wait Line.

D - Save Information on Disk

E - Call Information from Disk

F - Selftest of the Analysis Modules

Figure 13. Main Menu

Figures 14 and 15 show the menus used to setup the Snoop Modules before recording FASTBUS transactions. This menu provides a means of setting-up the front-end logic of Snoop Modules for different forms of recording. the Option D of Figure 14 is of particular interest. In this mode of operation, when the Snoop Modules are interfaced to a host computer, the recording process is completed only when all modules have stopped recording into their silo memory. In the case in which a Snoop Module is located in a FASTBUS segment and no transactions are occurring, this option allows the user to disconnect the Snoop Module from the Analysis System without having to change its internal setup. Also note that this menu consists of two switchable pages.

neesessaasessa e n ussa saassaasees SETUP FOR THE RECORDING OF FASTBUS TRANSACTIONS ANALYSIS MODULE NUMBER [n] А RECORD FASTBUS TRANSACTIONS В EXECUTE THE MENU OF ANALYSIS OF FASTBUS CYCLES RECORDED C CONNECTED TO THE ANALYSIS SYSTEM Option: [Yes/No] D TRIGGER SOURCE Option: [n] E 1 - Internal trap sequence 2 - External 3 - Record Command TRIGGER POSITION Option: [n] F 1 - Start of cycles recorded 2 - End of cycles recorded SET TRAP WORDS G H NEXT PAGE Also 1=Previous Menu Figure 14. First Page of the Setup for Recording Menu Option: [n] TRIGGER SEQUENCE Α 1 - Arbitration, address and data cycle 2 - Arbitration, address and a second address cycle 3 - Arbitration and a second address cycle 4 - Address and data cycle 5 - Address and second address cycle 6 - Address cycle Option: [n] В SAMPLING STROBE SOURCE 1 - FASTBUS transactions 2 - Internal clock (50 MHz) 3 - External clock TYPE OF CYCLE TO RECORD Option: [n] С 1 - All FASTBUS cycles 2 - Arbitration and address cycles D LAST PAGE Also 1=Previous Menu Figure 15. Second Page of the Setup for Recording Menu Figure 16 shows one example of the Trap Words Menu. This is a menu with different formats, depending upon the Trigger Sequence chosen. For example, if the trigger

allow the user to set only an address trap.

sequence chosen was just an Address Cycle, this menu will

лязаялалалалая M е n Цэээленнананая TRAP WORDS Sequence: Arbitration, address and data cycle A AL pattern for Bus Arbitration Trap Pattern = [00] Pattern = [00000000]B AD pattern for the Address Trap Mask = [FFFFFFF]C AD mask for the Address Trap D MS pattern for the Address Trap Pattern = [00]E MS mask for the Address Trap Mask = [FF]Pattern = [00000000]F AD pattern for Data Trap Mask = [FFFFFFFF].G AD mask for Data Trap Pattern = [00]H MS pattern for the Data Trap Mask = [FF]I MS mask for the Data Trap Also 1=Previous Menu

Figure 16. Trap Words Menu

Figure 17 shows the menu for the analysis of the FASTBUS transactions recorded into the silo memory. Options A, B and C are presently developed. Option C is useful when the user wants to compare the FASTBUS transactions recorded by one Snoop Module with the transactions recorded by another.

ANALYSIS OF THE FASTBUS TRANSACTIONS RECORDED

| A          | Record FASTBUS Transactions                                      |   |

|------------|------------------------------------------------------------------|---|

| В          | List of transactions from one Module                             | • |

| С          | List of transactions from two Modules                            |   |

| D          | Timing Diagram                                                   | • |

| Е          | Disassemble list of transactions                                 |   |

| Als<br>=== | o 1=Previous Menu                                                |   |

|            | Figure 17. Analysis of the FASTBUS Transactions<br>Recorded Menu |   |

The last menu developed is the menu to stop the recording process. It is shown in Figure 18. This menu is shown when the user activates the recording process (option B of Figure 14 and option A of Figure 17).

# STOP RECORDING MENU

A Stop Recording and Return to the Analysis MenuB Stop Recording and Return to the Setup Menu

Also 1=Previous Menu

Figure 18. Stop Recording Menu

The menus interact with the Snoop Module by means of a set of function subprograms. These function subprograms perform the following:

1. Setup the Snoop Modules.

2. Read the silo memory of the Snoop Modules.

3. Control the recording process.

4. Build different forms of tables to enable the user to analyze the transactions recorded.

A list of these function subprograms and their respective use is given below:

1. Function subprograms to set and read the arbitration trap: STATUS=AN\_F\_set\_trap\_arb\_AL (mod\_no,patt) STATUS=AN F get trap arb AL (mod\_no,patt)

source: STATUS=AN F set trigger src (mod no,trigger\_src)

- sequence: STATUS=AN\_F\_set\_trigger\_sequence (mod\_no,tr\_seq) STATUS=AN\_F\_get\_trigger\_sequence (mod\_no,tr\_seq) 5. Function subprograms to set and read the trigger

- another address trap: STATUS=AN\_F\_set\_trap\_dat\_add\_AD\_mask (mod\_no,mask) STATUS=AN\_F\_get\_trap\_dat\_add\_AD\_mask (mod\_no,mask) STATUS=AN\_F\_set\_trap\_dat\_add\_AD\_patt (mod\_no,patt) STATUS=AN\_F\_get\_trap\_dat\_add\_AD\_patt (mod\_no,patt) STATUS=AN\_F\_set\_trap\_dat\_add\_MS\_mask (mod\_no,mask) STATUS=AN\_F\_get\_trap\_dat\_add\_MS\_mask (mod\_no,mask) STATUS=AN\_F\_set\_trap\_dat\_add\_MS\_patt (mod\_no,patt) STATUS=AN\_F\_set\_trap\_dat\_add\_MS\_patt (mod\_no,patt) STATUS=AN\_F\_get\_trap\_dat\_add\_MS\_patt (mod\_no,patt) ATTUS=AN\_F\_get\_trap\_dat\_add\_MS\_patt (mod\_no,patt)

- trap: STATUS=AN\_F\_set\_trap\_add\_AD\_mask (mod\_no,mask) STATUS=AN\_F\_get\_trap\_add\_AD\_mask (mod\_no,mask) STATUS=AN\_F\_set\_trap\_add\_AD\_patt (mod\_no,patt) STATUS=AN\_F\_get\_trap\_add\_AD\_patt (mod\_no,patt) STATUS=AN\_F\_set\_trap\_add\_MS\_mask (mod\_no,mask) STATUS=AN\_F\_get\_trap\_add\_MS\_mask (mod\_no,mask) STATUS=AN\_F\_set\_trap\_add\_MS\_patt (mod\_no,patt) STATUS=AN\_F\_set\_trap\_add\_MS\_patt (mod\_no,patt) STATUS=AN\_F\_get\_trap\_add\_MS\_patt (mod\_no,patt) STATUS=AN\_F\_get\_trap\_add\_MS\_patt (mod\_no,patt) STATUS=AN\_F\_get\_trap\_add\_MS\_patt (mod\_no,patt)

- 2. Function subprograms to set and read the address

STATUS=AN F set start rec STATUS=AN F set stop rec STATUS=AN F get status rec (mod no) Function subprograms to build lists to analyze 10. the transactions recorded in the silo memory: STATUS=AN F analyze list one mod (mod no)

STATUS=AN F analyze list two mod (modA no,modB no)

Function subprograms to connect or disconnect

Snoop Module from the Analysis System:

STATUS=AN F set mod hiber (mod no)

STATUS=AN F set mod wake (mod no)

STATUS=AN F get mod dreams (mod no)

the recording process:

STATUS=AN\_F\_set\_trigger\_pos (mod\_no,trigger\_pos) STATUS=AN F get trigger pos (mod no, trigger pos) 8. Function subprograms to set and read the type of cycle recorded:

STATUS=AN F set type cycles rec (mod\_no,type\_rec)

STATUS=AN F get type cycles rec (mod no,type\_rec)

Function subprograms to control the execution of

9.

11.

- STATUS=AN F set strobe src (mod no, strobe src) STATUS=AN F get strobe src (mod no, strobe src) 7. Function subprograms to set and read the position of the trigger:

- Function subprograms to set and read the sampling strobe source:

- 6.

STATUS=AN\_F\_get\_trigger\_src (mod\_no,trigger\_src)

the

Each of these function subprograms returns to the caller routine a number (STATUS) indicating if the operation was successfully completed.

Figure 19 shows an example of one of the functions subprograms written. In 'this subprogram the command "Encode" translates a hexadecimal number to ASCII.

<u>Software Executed by the Snoop Modules When Connected</u> with the Host. When the Snoop Module is connected to the host computer, it executes software similar to that which it executes when it is connected to a terminal. The basic difference between the two modes of operation is in the form of communication, which is described in the next section.

The host computer sends Forth words and numbers to the Snoop Modules to control and read the Snoop Module. These words are similar to the words used when the Snoop is connected to a terminal, with the difference that numbers set the different options. When the host reads the setup of the Snoop Module, again, it reads numbers instead of messages. These numbers are the numbers specified in the menus (for example, see Fig. 14 and 15). There are some words which are used in both modes of operation - the first mode is when the Snoop Module is interfaced to a terminal, and the second mode when it is interfaced to a host. Figure 20 shows some examples of these words.

```

Integer*4 Function AN_F_set_trigger src

(mod_no,trigger src)

С

с

Description

С

е

Set the trigger source of the Snoop Module

с

С

Call Parameters

с

______

Integer*4

mod no

Integer*4

trigger_src

c

External Routine: Transmit data to the module.

С

С

External

AN N output data

С

Parameter Statements

С

C

_____

Include

'ANALYZER PAR.FOR/nolist'

Parameter

out char no = 9

С

с

Local Declarations

С

Integer*4

AN N out data buffer size

Character*(out_char_no) AN N_out_data buffer

Integer*4

ok

С

С

Data Statements

с

_____

Data

AN_N_out_data_buffer / ' TR-SRC!'/

AN N out data buffer size / out char no /

Data

с

с

Format Statement

______

с

100

Format(I1)

С

С

Executable Code

С

Encode (1,100,AN_N_out_data_buffer) trigger_src

ok = AN N output data (mod no,

AN N output data buffer,

AN_N_output_data_buffer_size)

if ( ok .ne. AN N success ) then

AN_F_set_trigger_src = AN_F_network_error

else

AN_F_set_trigger_src = AN F success

endif

return

end

Figure 19. Example of a Host Computer Function

Subprogram to Setup the Snoop Module

```

| n TR-SRCI | 7 | Set the trigger source<br>n = 1: Internal trigger source<br>n = 2: External trigger source<br>n = 3: Asynchronous trigger     |

|-----------|---|-------------------------------------------------------------------------------------------------------------------------------|

| n TR-POS! | - | Set the trigger position among the cycles<br>recorded<br>n = 1: Start of cycles recorded<br>n = 2: End of cycles recorded     |

| ?SS-SRC.  | ~ | Read the sampling strobe source set<br>n = 1: FASTBUS transactions<br>n = 2: Internal clock (50 MHz)<br>n = 3: External clock |

| n TP-L!   | ~ | Set the arbitration trap                                                                                                      |

n = pattern of the trap

Figure 20. Examples of Forth Words Used by the Host to Control and Read the Snoop Module

The Communication Among the Host and the Snoop Modules. amount of data exchanged between the host computer and The the Snoop Modules is small and can be done adequately at low data rates (for example, 9600 bits per second). Therefore, a simple form of communication was developed using serial lines. Another feature provided by this simple communication technique is the ability to send broadcast This is important to synchronize the operations messages. of different Snoop Modules.

The basis of this serial communication technique is the Binary Synchronous Communication (BISYNC) protocol from International Business Machines, which "provides a set of rules for synchronous transmission of binary coded data" (8). To develop this serial communication protocol, the control characters of BISYNC, as well as, a subset of its

data transfer rules were used. Figure 21 shows the interconnection of the host computer with the Snoop Modules.

Figure 21. The Serial Interconnection of the Host and the Snoop Modules

The protocol consists of the following:

- The communication is asynchronous and uses only ASCII characters.

- 2. A centralized multipoint environment is used, with the host being the control station and the Snoop Modules the tributary stations.

- 3. The control station regulates all transmission by means of polling and selection. By sequentially polling each tributary station, the control station directs the incoming message traffic. The outgoing traffic is regulated by the control station selecting the desired tributary station to receive the message. All transactions are between the

control station and the selected tributary station.

4. The operation to start any communication is accomplished by the control station transmitting the following message:

[EOT Polling'or selection ENQ PAD] 5. The polling or selection field is made up of 3 characters which contain the necessary information to perform polling or selection with different The first two characters are the address modules. of the tributary station in ASCII and the third is P for polling and a S for selection. If the а module number is smaller the 10, it is sent a space and the decimal module address.

- 6. The control or the tributary station can be in the receiving or transmitting mode, depending on whether data or control must be received or transmitted by the station.

- 7. The control station can send only one block of text per selection. If it has to send more characters than can be supported by the block size, it has to select the tributary again for additional transmission of another message block.

- 8. The meaning of the control characters for the FASTBUS logic analyzer serial communication protocol are as following:

- a. STX START OF TEXT: This character precedes a block of text characters. Text is that portion of a message treated as an entity to be transmitted through to the ultimate destination without change.

- b. ETX ~ END OF TEXT: The ETX character terminates the text. ETX requires a reply indicating the receiving station status, with the exception of the broadcast message.

- c. EOT END OF TRANSMISSION: This character indicates the end of a message transmission, which may contain one or more text messages. It causes a reset of all stations on the line. It is also used to respond to a poll when the polled station has nothing to transmit.

- d. ENQ ENQUIRY: The ENQ character is used to obtain a repeat transmission of the response to a message block if the original response was garbled or was not received when expected. It also indicates the end of a poll or selection sequence.

- e. ACK AFIRMATIVE ACKNOWLEDGEMENT: This reply indicates that the previous block was accepted without error and the receiver is ready to accept the next block of transmission.

- f. NAK NEGATIVE ACKNOWLEDGEMENT: NAK indicates that the previous message was received in error and the receiver is ready to accept a retransmission of the erroneous block.

- g. PAD PAD CHARACTER: A PAD character is added following each transmission to ensure that the last significant character is sent before the data set transmitter turns off. BELL character ( hex '07' ) is used as PAD.

- 9. The parity bit is use to validate the characters received by the tributary and control station.

- 10. Address 0 is the broadcast address. All tributary stations recognize this address and accept the text if it is correct. There is no reply from the tributary stations.

- 11. A timeout is used to limit the waiting time tolerated by the control station to receive a reply. When a timeout occurs, the control station will again send its previous message and wait for the reply. If a specific number of timeouts occurs for the same message, the control station assumes that the tributary is damaged or disconnected from the network, and aborts the transmission.

- 12. The control station checks for errors in the transmission, or replies, indicating that errors are being detected by the tributary stations. If these errors happen repeatedly, it aborts the

operation and reports the fault. Some examples of this error detection are the control stations repeatedly receiving NAK as replies when a text is being transmitted or repeatedly receiving ENQ as an answer for an ACK after a text was successfully received.

Based on these rules, the process for reading some data from the Snoop Modules is the following: first the host has to select the Snoop Module and indicate which data it needs to read; after this it has to poll the Snoop Module and read the data. Figures 22, 23 and 24 show examples of this protocol.

CTRL[EOT 2 S ENQ PAD][STX Text ETX PAD]TRIB\_1..TIRB\_2[ACK PAD]CTRL..[ENQ 1 P ENQ PAD]..TRIB\_1 ....TRIB\_2 ..<[ACK PAD]</td>[STX Text ETB PAD]CTRL..<[ACK PAD]</td>[ACK PAD][ACK PAD]

TRIB\_2 .. [STX Text ETX PAD] [EOT PAD]

Figure 22. Typical Data Link Message Traffic

CTRL [EOT 2 S ENQ PAD][STX Text ETX PAD]..TRIB\_2[ACK PAD][NAK PAD].

CTRL ..[STX Text ETX PAD] [EOT PAD] TRIB 2 .. [ACK PAD]

Figure 23. Data Link with a NAK

CTRL [EOT 1 S ENQ PAD] [STX Text ETX PAD] .. (Timeout) TRIB\_1 [ACK PAD] ..

CTRL ..[STX Text ETX PAD] [EOT PAD] TRIB 1 .. [ACK PAD]

Figure 24. Data Link with the Occurrence of Timeout

Two function subprograms were developed for the host which enable it to communicate with the Snoop Modules: a function to send data to the modules and another to read data from the modules. These functions are invoked by the following:

STATUS = AN\_N\_input\_data(mod\_no,in\_buffer,in\_buffer\_size,

no char received)

STATUS = AN\_N\_output\_data(mod\_no,out\_buffer,out\_buffer\_size)

Each of these function subprograms returns a number (STATUS) to the caller routine indicating if the operation was successfully completed. If some error was detected in

the operation, this number corresponds to the error detected.

Figure 25 shows part of the software that performs the operation which starts the communication with a tributary. Note that the System Service Routines of the VAX/VMS computer (9) are called to perform the following tasks:

- Assigning a serial port to this process (sys\$assign).

- Transmiting and receiving of the characters exchanged with the Snoop Module (sys\$qio and sys\$qiow).

- 3. Checking for timeout (sys\$schdwk).

- Causing the process to go into hibernation (sys\$hiber).

- 5. Stoping the process in case of error in one of the previous operations (call lib\$stop).

As it has already been explained, the Snoop Module has to be able to interface to a terminal or to the host. In order to accomplish this goal, the communication protocol was made switchable between one mode which performs communication with a terminal and another mode which permits communication with the host (see Appendix C).

The protocol necessary to perform the communication directly with a terminal already exits in the Forth software package resident on the Snoop Module - it is the standard way that Forth communicates with the user.

Assign the serial port SNOOP\$PORT to this ¢ process if it was not previously assigned. с С if ( .not. assign\_done ) then ok = sys\$assign ('SNOOP\$PORT', serial\_port, ,) if ( .not. ok ) call lib\$stop ( ok ) assign done = .true. endif с Queue a read to the serial port to receive the с answer from the tributary. When the answer is С С received, an interruption is generated and the subroutine "AN N sel int" or "AN N poll\_int" is С executed, depending if it is selection or polling. С с ok=sys\$qio (,%val(serial port) , %val(io\$ ttyreadall .or. io\$m purge) , %ref(io status\_block) AN N sel\_int , , !or AN N poll int %ref(in buffer),%val(in buffer size) , , %ref(terminator mask) , , ) с с Send the inicialization message selecting or polling the tributary station: [EOT mod no S or P ENQ PAD]. С С byte count = 1out buffer (byte count) = EOT byte count = byte count + 1 out\_buffer (byte\_count) = mod\_no\_ascii (1:1)

byte\_count = byte\_count + 1 out\_buffer (byte\_count) = mod\_no\_ascii (2:2) byte count = byte count + 1 lor 'P' out buffer (byte count) = 'S' byte count = byte count + 1 out\_buffer (byte\_count) = ENQ byte\_count = byte\_count + 1 out buffer (byte count) = PAD ok=sys\$qiow (,%val(serial\_port) , %val(io\$\_writevblk.or.io\$m\_noformat) , %ref(io\_status\_block) , , , %ref(out buffer) , %val(byte count) if ( .not. ok ) call lib\$stop ( ok ) с Wait for the answer by turning the process into с hibernation. Schedule a wake up to test timeout. С The timeout flag is turn false in the int. routine. С c timeout flag = .true. ok = sys\$schdwk ( , , timeout\_period , ) if ( .not. ok ) call lib\$stop ( ok ) ok = sys () Figure 25. Part of the Communication Functions for the VAX

#### CHAPTER V

#### FUTURE DEVELOPMENTS

There are more developments involving the FASTBUS Logic Analyzer which Fermilab plans to pursue in the next year. It is anticipated that the use of this FASTBUS logic analyzer facility will point towards other implementations which test and diagnose errors on FASTBUS and are not presently identified.

Part of these new developments were pointed out in the discussion about the menus in Chapter IV. These future developments are:

- 1. Routines to allow the Snoop Module to control the assertion of the FASTBUS Wait line.

- Routines to save and recall information from the disk of the host computer.

- Routines to provide selftest capability to the Snoop Module.

- 4. Routines to show the FASTBUS transaction recorded in the silo memory in timing diagram form and in a FASTBUS disassembled form. As an example of a FASTBUS transaction expressed in disassembled form see Figure 26.

47

| SIAD | AlagGKar | AL EGrd | A D      | PApe | SRwt | MSss | OPERATION     |

|------|----------|---------|----------|------|------|------|---------------|

| 000  | 0 0 1 0  | 11 0 0  | 00000017 | 1 1  | 0 0  | 10   | Primary Add   |

| 001  | 0 0 1 0  | 11 0 0  | 00000000 | 1 1  | 0 0  | 20   | Secondary Add |

| 002  | 0 0 1 0  | 11 0 1  | 00A20000 | 01   | 0 0  | 00   | Randon Read   |

| 003  | 0 0 1 0  | 11 0 0  | 00000018 | 1 1  | 0 0  | 0 0  | Primary Add   |

| 004  | 0 0 1 0  | 11 0 0  | 00004000 | 1 1  | 00   | 22   | ERROR=Parity  |

| 005  | 0 0 1 0  | 11 0 0  | 12AC3280 | 1 1  | 0 0  | 0 0  | ERROR=Timeout |

4

.

Figure 26. Example of FASTBUS Transaction Expressed in Disassembled Form

### CHAPTER VI

#### CONCLUSIONS

The FASTBUS Analysis System described in this thesis was developed at Fermilab. It was incorporated in systems similar to the configurations shown in Figures 8 and 11. They were used to test the ability of this Analysis System to record FASTBUS messages being exchanged between Masters and Slaves. The Analysis System worked properly.

The data acquisition system being built for the Collider Detector at Fermilab is already in operation in a simple configuration and a detailed implementation is presently being completed. On October 13, 1985, it was used for detecting a proton-antiproton collision for the first time.

From the experience gained in tracing software and hardware faults in the FASTBUS of the present configuration of this data acquisition system, it has been established that this Analysis System will be very useful in diagnosing various classes of FASTBUS faults.

The complexity of Electronic Systems is increasing very rapidly due to the need for increased processing speed and the low cost of electronic hardware. Other distributed processing systems which use techniques similar to this data acquisition system are being developed around the world. The work developed in this thesis is an approach that can be used by these other systems to trace faults on their system buses.

49

APPENDIX A

. . .

.

•

#### FASTBUS DESCRIPTION

This Appendix is a copy of parts of the FASTBUS specification manual (1).

#### Introduction

FASTBUS is a standardized modular multi-master data-bus system for data acquisition, data processing and control applications. A typical FASTBUS system consists of multiple Crate Segments which operate independently but connected together for passing data and other information. FASTBUS can operate asynchronously using a handshake protocol to reliably accomodate different speed devices without prior knowledge of their speed. It can also operate synchronously without handsake for transfer of data blocks at maximum speed. It also has a multiplexed bus of data and address of 32 lines. These basic characteristics give to FASTBUS Systems a high throughput and speed of operation.

Most FASTBUS design features stem from a consideration of the requeriments of contemporary data acquisition systems. The need for high speed is met by providing for parallel operation of many processors which can communicate with each other as well as with data acquisition and control devices. The communication protocol used by processors and devices has a large data and address field and is defined in an implementation-independent manner so as to be able to take advantage of advances in technology. The need for flexibility is met by a modular design which readily permits

many options in system configuration.

Modular instrumentation systems are distinguished by method used to interconnect the devices that form the the system. Mechanical, electrical, and logical aspects of the connection have to be specified. The electrical connections are made by a set of signal lines called a SEGMENT. While FASTBUS DEVICES can be simply connected by CABLE SEGMENTS, such an arrangement may incur speed penalties. The more usual situation is that the required functionality at a given location is attained by a number of MODULES grouped together in a CRATE in order to share a common backplane bus (Fig. 1). This bus, called a CRATE SEGMENT or SEGMENT, like the CABLE SEGMENT forms a logical element of a FASTBUS system.

Using the FASTBUS protocol, a SEGMENT functions as an interconnecting one or more MASTER DEVICES autonomous bus with a number of SLAVE DEVICES. All bus operations involve MASTER-SLAVE relationship between the initiator, which а must be a MASTER, and the responder, which must be a SLAVE. MASTER is capable of requesting and obtaining control of Α the SEGMENT to which it is connected in order to communicate with the SLAVE. If the communication is with another MASTER then, for the duration of the operation, the responding MASTER acts as a SLAVE. A SLAVE cannot gain bus mastership but can make a Service Request that a MASTER on the same SEGMENT can use to initiate a procedure to service the request. MASTERS have a more versatile interrupt mechanism

51

-

in that they can gain bus mastership and write an interrupt message to an interrupt service device. With multiple MASTERS on a SEGMENT, techniques must be provided to resolve concurrent requests for use of the bus. Each MASTER is assigned an Arbitration Level to use during Arbitration Cycles. In response to timing signals from the SEGMENT Arbitration Timing Controller, circuitry in each MASTER determines which of the contending MASTERS will next be granted bus mastership. No time penalty is usually associated with this arbitration procedure since the next MASTER can be selected before the current MASTER completes its operation.

Multiple MASTERS on a single SEGMENT share a common bus. Contention for use of this bus may reduce throughput as seen by a given MASTER because of the time its spends waiting to gain Mastership of a busy bus. Since SEGMENTS operate independently, distributing the MASTERS among several SEGMENTS can reduce the contention problem and increase throughput to the extend that the information needed by each MASTER can be localized on its SEGMENT.

A MASTER on one SEGMENT must also be able to quickly communicate with a SLAVE on another SEGMENT. This ability is provided by SEGMENT INTERCONNECTS (SIs) which temporarily link independent SEGMENTS (Fig. 2). All SEGMENTS through which the operation passes must be available at the same time in order to complete an intersegment operation. The arbitration mechanism, along with circuitry in each SI,

extends the resolution of bus contention problems to off- as well as on-SEGMENT MASTERS. Since one SEGMENT can be linked to of number of different any а SEGMENTS, system configurations can be implemented which optimize time-critical data paths.

While most, if not all, MASTERS will have some processing ability, the FASTBUS system design also envisages the connection of large and small computers to the system. connection is made by a PROCESSOR INTERFACE which Such a gains entry to the FASTBUS system through either a CABLE or a CRATE SEGMENT (Fig. 2). System requirements dictate that each system contain one processor which has complete knowledge of the structure of the system. In particular, it must be able to access every SEGMENT of the system and know how the SEGMENTS are to be interconnected. This processor, called the HOST, initializes the system by telling each side SI what operations it is to pass on to its other of each SEGMENT. By using GEOGRAPHICAL ADDRESSING, the HOST can ascertain the physical location and type of each DEVICE in the system and, as needed, assign LOGICAL ADDRESSES to the LOGICAL ADDRESSES allow a DEVICE to DEVICES. use an INTERNAL ADDRESS Field matched to its needs which is independent of position within a SEGMENT.

The principal characteristics and capabilities of FASTBUS can be summarized as follows:

- Speed limited only by propagation and logic delays (typically better than 10 MHz for ECL)

- 2. Large Address and Data Fields (32 bits)

- 3. Segmented Bus to allow parallel processing

- 4. System-wide commun

- 5. Block transfers with or without handshake

- 6. Uniform system-wide protocol

- 7. Interrupt and arbitration features.

The FASTBUS operations make use of a multiline bus whose signal assignments are as indicated in Table 3. A CABLE SEGMENT consists of the group of 60 lines at the top of the list while a CRATE SEGMENT includes in addition the other listed lines as well as power lines.

#### FASTBUS Operations

Most FASTBUS operations begin with a MASTER requesting and being granted bus mastership. The MASTER then selects a SLAVE by a primary address cycle and follows this by any number of data transfer cycles after which the bus is released.

The primary address cycle is started by the MASTER asserting the SLAVE'S address on the 32 Address Data (AD) lines followed by Address Sync (AS) (see Fig. 27). This assertion of the address word sets up a path, through SEGMENT INTERCONNECTS if necessary, between MASTER and SLAVE. When the SLAVE recognizes its address, it responds with the Address Acknowledge signal (AK).

> -.

| Mnemonic | Signal Name                    | Use | Number      |

|----------|--------------------------------|-----|-------------|

| AS       | Address Synchronism            | Т   | 1           |

| A K      | Address Acknowledge            | Т   | 1           |

| EG       | Enable Geographical            | СТ  | 1           |

| MS       | Mode Select                    | С   | 3<br>1      |

| R D      | Read                           | С   |             |

| A D      | Address/Data                   | I   | 32          |

| PA       | Parity                         | I   | 1           |

| PE       | Parity Enable                  | I   | 1           |

| SS       | Slave Status                   | I   | 3           |

| DS       | Data Synchronism               | T   | 1           |

| D K      | Data Acknowledge               | Т   | 1           |

| WT       | Wait                           | А   | 1           |

| SR       | Service Request                | А   | 1           |

| RB       | Reset Bus                      | A   | 1           |

| BH       | Bus Halted                     | C   | 1           |

| AG       | Arbitration Grant              | ТА  | 1           |

| AL       | Arbitration Level              | IA  | 6           |

| AR       | Arbitration Request            | A   | 1           |

| ΑI       | Arbitration Request<br>Inhibit | CA  | 1           |

| GK       | Grant Acknowledge              | ΤA  | 1           |

| ТX       | Serial Line Transmit           | S   | 1           |

| RX       | Serial Line Receive            | S   | 1           |

| GA       | Geographical Address           | F   | 5           |

|          | Pins (position encoded,        |     |             |

|          | not bussed)                    |     |             |

| ТР       | T Pin (not bussed)             | Х   | 1           |

| DL       | Daisy Chain Left               | Х   | 3<br>3<br>8 |

| DR       | Daisy Chain Right              | X   | 3           |

| TR       | Terminated Restricted<br>Use   | Х   | 8           |

| UR       | Unterminated Restricted        | х   | 2           |

|          | Use                            |     | <b>د</b> .  |

| FΡ       | F Pins (Free use, not          |     | 4           |

| ď        | bussed)<br>Reserved            |     | · 5         |

| R        | Nedel ven                      |     | 2           |

## Table 3. FASTBUS Signals

٩

-----

...

#### Table 3.( continued )

#### Description of Symbols

| Т  |    | Timing for address and data cycles              |

|----|----|-------------------------------------------------|

| С  | =  | Control for address and data cycles             |

| I  | =  | Information for address and data cycles         |

| СТ | =  | Control and timing                              |

| А  | 52 | Asynchronous - timing not directly related      |

|    |    | to data transfers                               |

| ТΑ | a  | Timing for Arbritation bus                      |

| IA | =  | Information for Arbitration bus                 |

| CA | =  | Control for Arbitration bus                     |

| S  | =  | Serial data, timing independent of parallel bus |

| F  | =  | Fixed information - constant                    |

| Х  | =  | Special Purpose                                 |

The protocol requires that AS and AK remain asserted until the operation is completed.

Figure 27. Basic Handshake Read Operation (As Seen by Master)

On receipt of the AK response from the SLAVE. the MASTER removes the address information from the AD lines and uses these lines for data during the ensuing data transfer cycles. After the AS/AK lock between MASTER and SLAVE has thus been established, a Read operation can be initiated by MASTER asserting the Read (RD) and Data Sync (DS) lines the as in Fig 27. The SLAVE responds by placing data on the ΑD

56

lines and issuing DK which is used by the MASTER to latch the data. For a Write operation, the MASTER asserts data on the AD lines and follows this assertion by the Data Sync (DS). The SLAVE responds by issuing a Data Acknowledge (DK). The operation is terminated by the MASTER removing all its signals, including AS, from the bus. The SLAVE, sensing the removal of AS, removes all its signals including AK.

Since Address and Data Cycles are easily distinguishable, the three Mode Select lines MS<2:0>, are used by the MASTER to modify the meaning of the address information and to independently specify the type of data transfer. In a primary address cycle, control or data space can be specified as well as single or multiple listener (Broadcast) mode. In a data cycle, random data, secondary address, or handshake or pipelined (non-handshake) block transfer can be specified.

Similarly the three Slave Status information lines, SS<2:0>, are used to indicate the success or reason for failure of an Address or a Data Cycle. Addressing difficulties can occur at SEGMENT INTERCONNECTIONS because the SI does not respond (Network Failure) or cannot gain access to its Far-side SEGMENT (Network Busy) or gets preempted by a higher priority operation (Network Abort). lockup caused by unused addresses on the destination Bus SEGMENT are avoided by timers in the MASTER and in the SI which places the address on the destination SEGMENT.

During a Data Cycle, in addition to being able to indicate that it can either accept no more data or has no more data to send, a SLAVE can also signal that it is currently busy or that it has detected one of several classes of error.

#### Arbitration for Bus Mastership

One of the most important requirements of a multi-processor system is a method for allocating control of the SEGMENTS to the various MASTERS which may be contending for bus Mastership simultaneously. Part of the circuitry to accomplish this, which resides on each independent SEGMENT, is called the Arbitration Timing Controller (ATC).

bus lines are dedicated to SEGMENT Ten priority arbitration. Each master is assigned a six-bit Arbitration Level. Masters wishing to gain bus mastership assert the Arbitration Request line (AR). If the Grant Acknowledge, GK, line is not asserted, the ATC starts an Arbitration Cycle by asserting the Arbitration Grant, AG, signal. Requesting Master respond by asserting their arbitration levels on to six Arbitration Level Lines AL<5:0>. On each the Arbitration Level line an asserted bit will override anv non-asserted bits. Each requester continually compares its Arbitration Level with the code on the AL lines bit-by-bit from most to least significant positions. If a requester detects a bit on the bus which it is not asserting, it the bus all of its own bits of lesser removes from

significance. After a time determined by the ATC, only the highest Arbitration Level remains asserted on the AL lines and each competitor knows if it has won or lost. When the Arbitration Timing Controller has determined that the bus is completely free (AS=AK=WT=GK=0) it stops asserting AG and the winning Master responds by asserting GK and assuming bus Mastership. The MASTER continues to assert GK until it is willing to allow another Arbitration Cycle. This is usually after the last Address Cycle of its sequence of operarions thus allowing the next MASTER to be selected before the current MASTER has finished its Data Cycles.

Of the 64 possible priority codes, zero is not used is easily confused with an idle bus. Codes 1 because it through 31 are available for use within the SEGMENT, and 32 through 63 are available for use as "system" priorities for unique assignment within communicating parts of a system. The Local priorities 1~31 must be assigned uniquely to DEVICES within a given SEGMENT, but can be reused on every When a SEGMENT INTERCONNECT connects a MASTER to SEGMENT. another SEGMENT, the Level used for arbitration on the second SEGMENT will normally be that of the SI rather than that of the originating MASTER. However, if one of the priorities was used by originating MASTERS, the SI system will propagate that priority onto the second SEGMENT, which is free to do since the system priorities are unique it along a route. The system priorities can be useful in preventing undue delay for important Broadcasts, and can

help expedite important messages which might otherwise suffer from fluctuating priorities as they form paths through the system.

No interruption or preemption of the current operation is possible. A MASTER is free to keep the bus as long as it wishes. If it sees AR=1 while AS=AK=1, it knows that other MASTERS in the system are being blocked by the current operation. The controlling MASTER should normally release bus within a reasonable time in order to allow other the MASTERS to acquire bus Mastership. It should allow either one Arbitration Cycle or a random Retry Delay to occur before again requesting bus Mastership. The general solution to the problem of contention and deadlock in FASTBUS is to give up and retry after a random delay.

### Control and Status Registers

Certain registers and functions in DEVICES need to he separated in address space from the normal data registers in a way which provides some protection from accidental access which does not interfere with the allocation and of addresses to the normal data portions of the DEVICES. For example, two memory DEVICES should be able to have their addresses set so that the memories are adjacent in address space, allowing them to be used as one larger memory. However, they may contain control registers and status registers associated with memory protection or error detection and correction, and these registers must also be

accessible. Furthermore, it is desirable that DEVICES have basic status and information registers in standard locations so that they can be readily accessed by standard shared programs.

The method chosen to accomplish this is to select control/status register (CSR) space in a primary address cycle by suitable coding of the MS lines. This is followed by a secondary address cycle to select a register in CSR space, and a data cycle to transfer to or from the registers. Secondary addressing provides a full 32-bit address for use within a DEVICE, which is enough address space so that it can easily be allocated in standard ways without fear of a shortage. Standard locations in dedicated CSR registers are specified for all the usual control and status bits. DEVICES are required to contain an identifier unique to the DEVICE type which is used during system This identifier is located in initialization. status register 0 so that even simple DEVICES with no address decoders can respond correctly with little added cost.

#### Segment Interconnects

A SEGMENT INTERCONNECT monitors the activity on the two SEGMENTS it connects, waiting for an address to appear which is in the set of addresses it has been programmed to recognize. It responds to a recognized address asserted on one of the SEGMENTS (Near side) by requesting use of the other SEGMENT (Far side) and asserting the given address on

that SEGMENT when it gains control. The two SEGMENTS remain together until the operation is complete. locked The address asserted on the Far side may, in turn, be recognized SEGMENT INTERCONNECT and may be passed to yet by another another SEGMENT. An arbitrary number of SEGMENTS can be needed for a given operation. linked as The address contains all the information needed to direct the appropriate SIs to form the correct connections.