## A 3D FPGA Track Segment Seeding Engine Based on the Tiny Triplet Finder

Jinyuan Wu Fermilab Sept. 2021

FERMILAB-SLIDES-21-108-E

This manuscript has been authored by Fermi Research Alliance, LLC under Contract No. DE-AC02-07CH11359 with the U.S. Department of Energy, Office of Science, Office of High Energy Physics.

## Introduction

- An exercise of implementing a 3-hit 3-D track segment seeding engine based on the Tiny Triplet Finder is presented.

- It is intended to group hits into track segments and to feed into later Kalman filtering stage.

- The silicon resource consumption of the seeding engine is small, and it can be put into a low-cost FPGA.

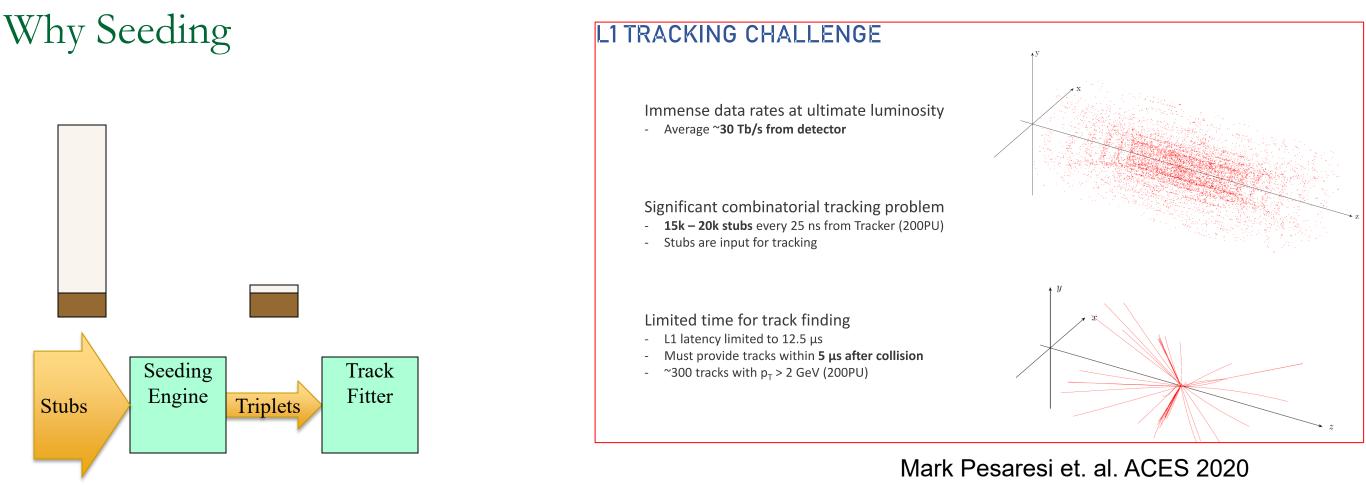

In our work, we use CMS L1 tracking Hybrid Algorithm as the example because it is challenging. But this work is not in official CMS project

#### Tracking in Multilayer Detectors

Andrew Hart et. al. 2020

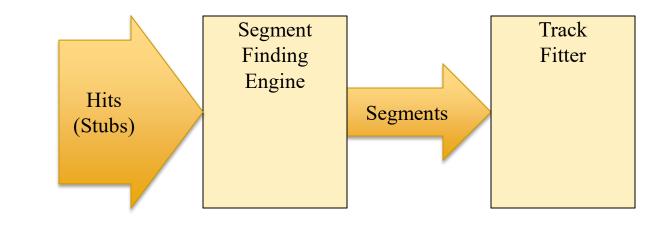

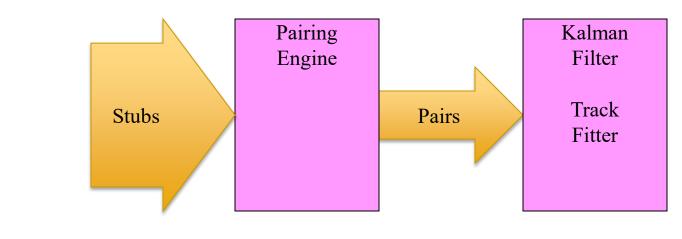

- Well accepted tracking approaches take the following stages:

- Hits or stubs are first grouped into track segments.

- Track segments are fitted into tracks.

### The CMS L1 Tracking Hybrid Algorithm

Andrew Hart et. al. 2020

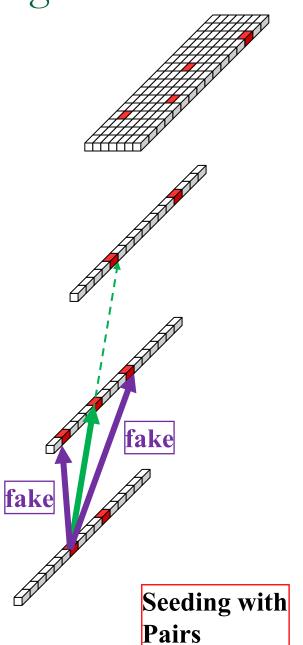

- Hits from different layers are first paired

- Track segments with paired hits are extended.

- Hits are fitted into tracks.

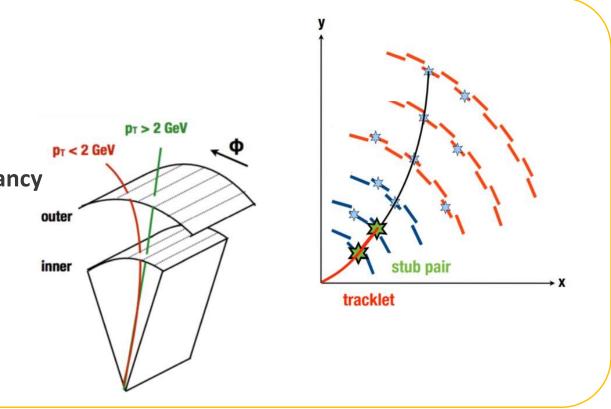

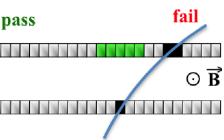

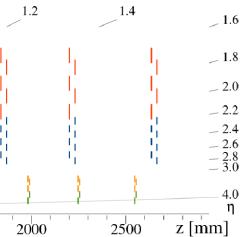

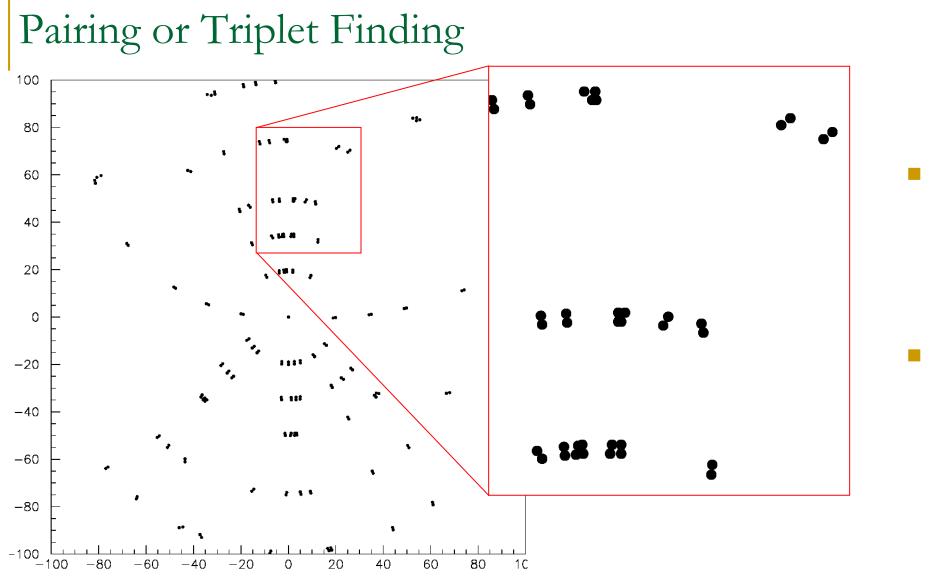

### Pairing

- Seeds (tracklets) are generated from **pairs of layers**

- Layer pairs selected to give full coverage in  $\eta$ , including **redundancy**

- Seeding step **massively parallelised** by internal geometrical partitioning & stub organisation (Virtual Modules - VMs)

Mark Pesaresi et. al. ACES 2020

#### The CMS L1 Tracking Hybrid Algorithm: find a **pair** => find third => fit and find others

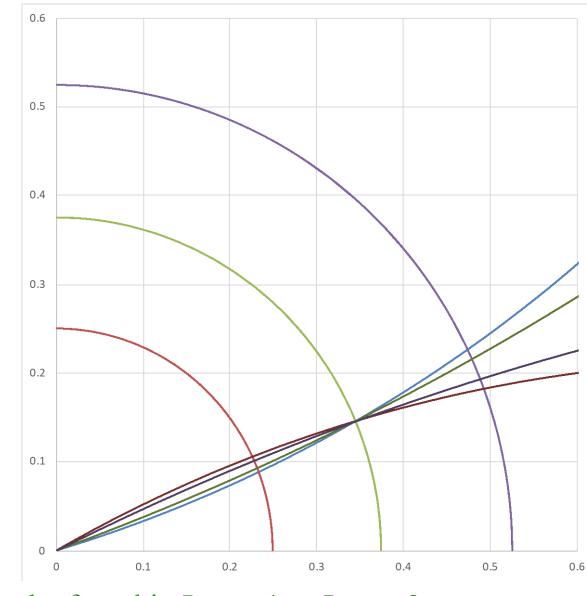

#### Pairing Stubs 1.2 1 0.8 0.6 0.4 0.2 0.2 0.4 0.6 0.8 1.2 1 0

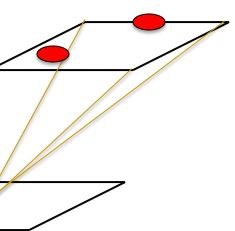

- For any stub in Layer 2, a range in phi and z must be searched in Layer 1 or/and Layer 3.

- Fake pairs may occur.

triplets of stubs becomes necessary.

Wu et. al. 2004 https://indico.cern.ch/event/418639/contributions/1018451 /attachments/868833/1216631/lowpt\_lecc2004p.pdf

"stub  $1 \div 4 mm$ ≤ 100 µm

#### If the separation of silicon sensor layers were large ( $\sim 10 \text{ mm}$ ), then stub pairing would be sufficient.

## Given the separation of $\sim 4 \text{ mm in}$ PS and 2S module, correlating

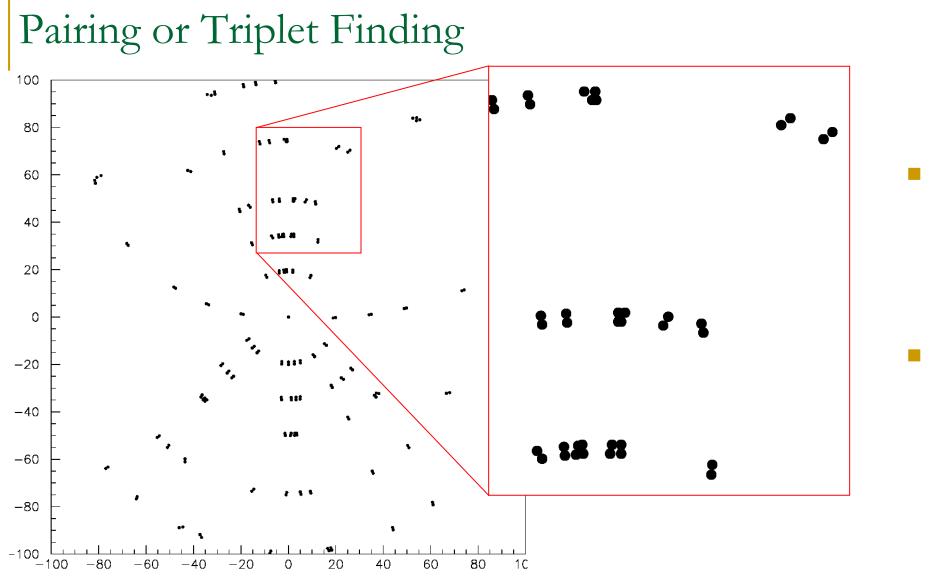

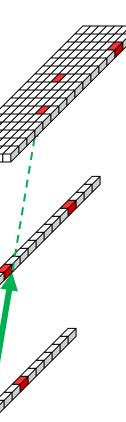

#### From Pairing to Triplet Seeding

- Simple pairing will creates more fake hit pairs, which must be eliminated in later stages.

- When three or more hits (stubs) are picked up together in triplet seeding stage, less fake segments are expected.

#### Seeding with Triplets

### Triplet Finding

- If three hits can be correlated together in a single action, would that be useful in the Hybrid Algorithm?

- It seems that the triplet finding is more natural for:

- Displaced track finding

- Beam-spot constraint tracking

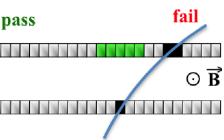

- Stub pairing won't eliminate stubs not associated with a high Pt track.

- Using three layers or more to most eliminate fake stubs in the seeding engine.

Triplet seeding is good. The algorithm is straightforward. The challenge is how to fit it into FPGA.

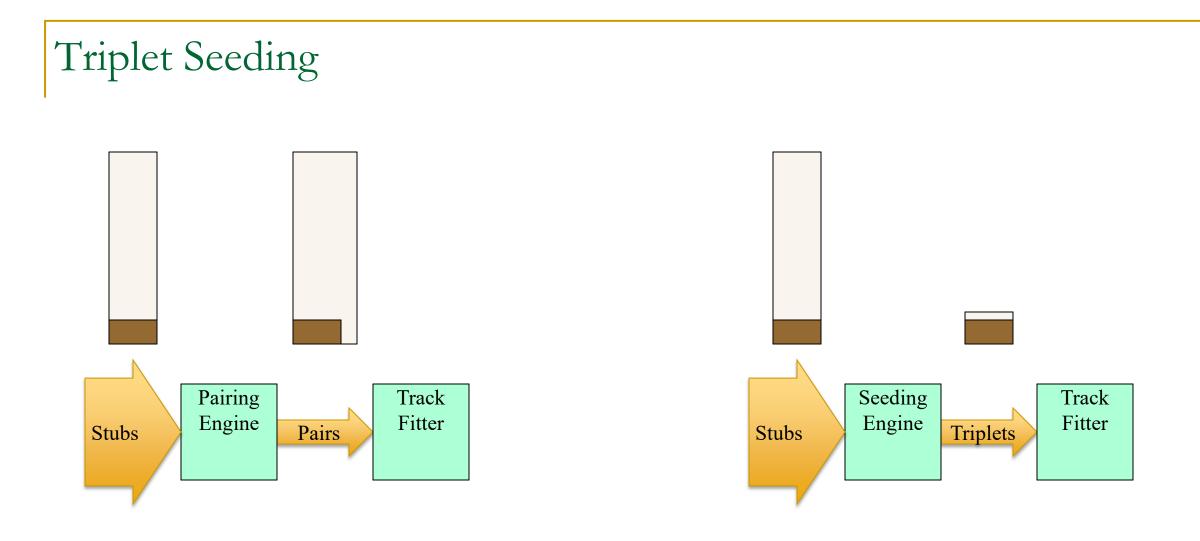

# **Tiny Triplet Finder:** -- A low resource usage scheme

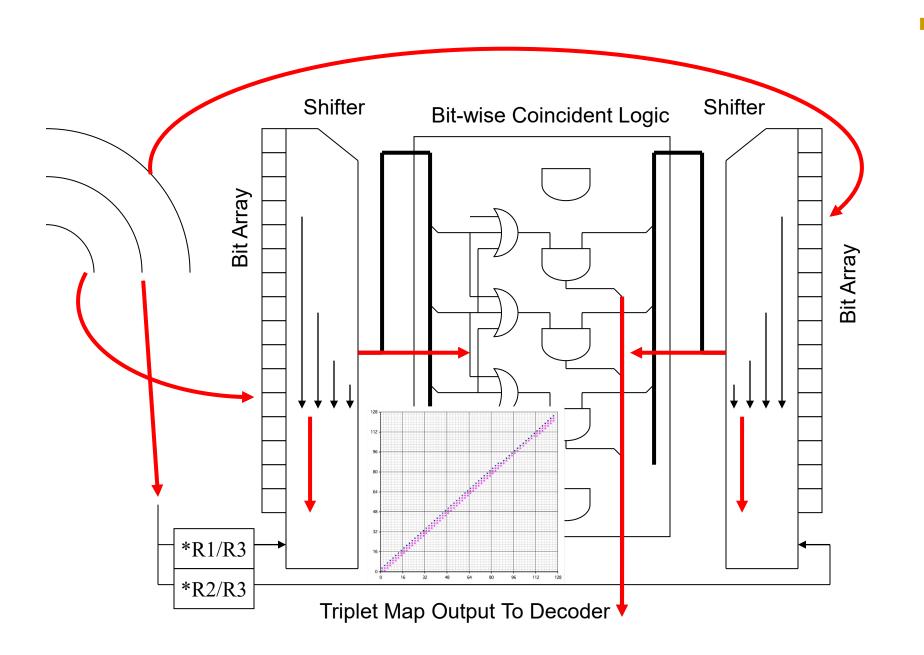

#### The Tiny Triplet Finder for Cylindrical Detector Geometry

- The Tiny Triplet Finer is a scheme to reuse a single set of track road coincidence logic for whole detector.

- It uses shift (or rotate) to bring bit arrays to feed the track road coincidence logic.

#### General Structure of the Tiny Triplet Finder

- includes:

- Shifters

#### A typical Tiny Triplet Finder

Bit arrays for different layers of the detector.

Bitwise coincidence logic.

# An Implementation Exercise

#### An Implementation Exercise Using CMS L1 Tracking as Exampl

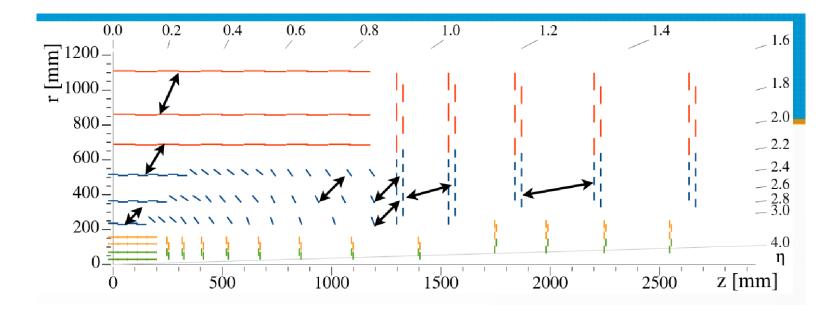

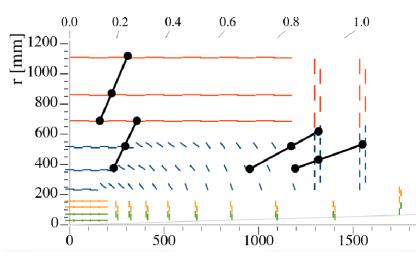

• The detector in the exercise have the same radii and lengths as CMS Outer Tracke

| ole |   |        |  |

|-----|---|--------|--|

| 0.  | ξ |        |  |

| /   | _ |        |  |

|     |   |        |  |

|     |   |        |  |

|     |   |        |  |

|     |   |        |  |

| •   |   |        |  |

| er  |   |        |  |

|     |   | <br>15 |  |

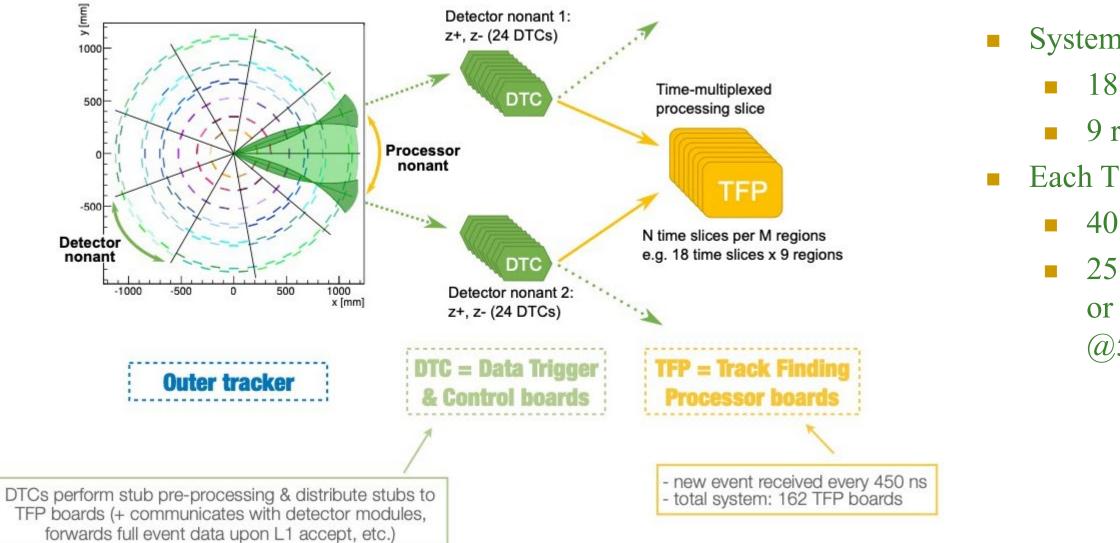

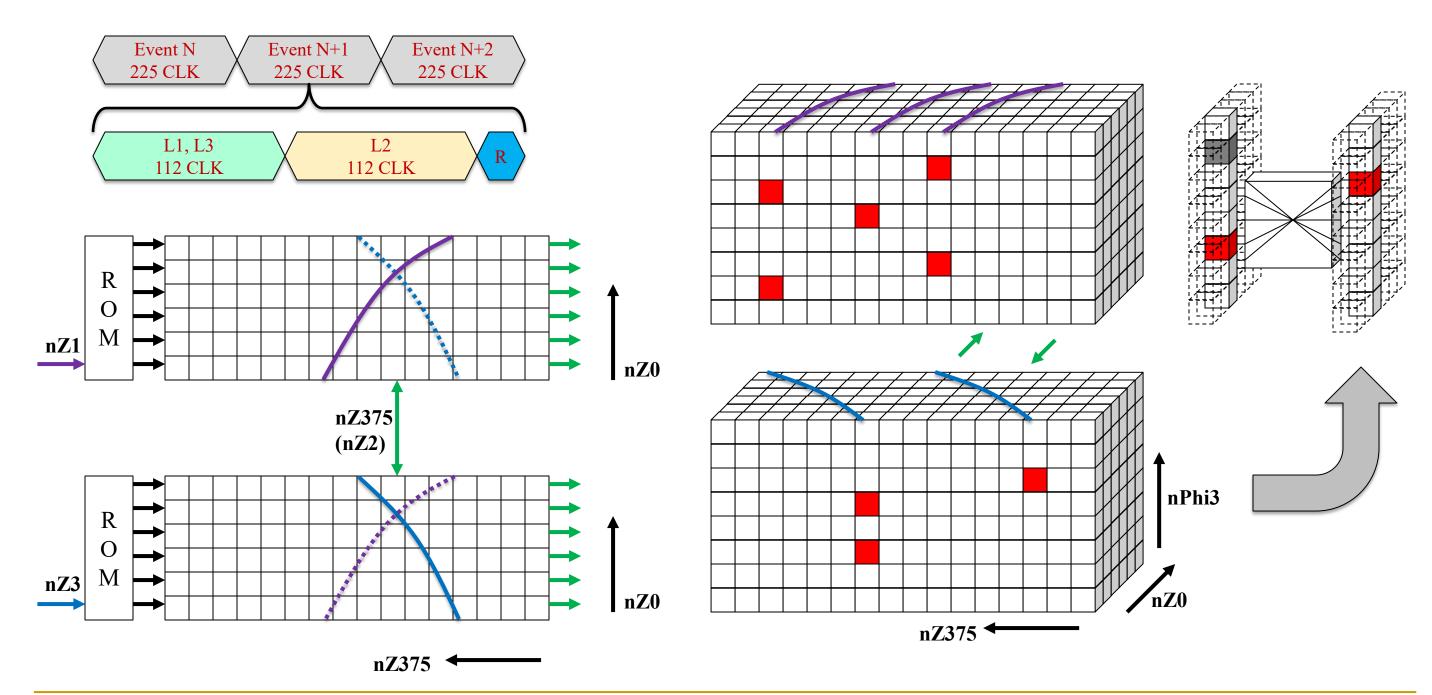

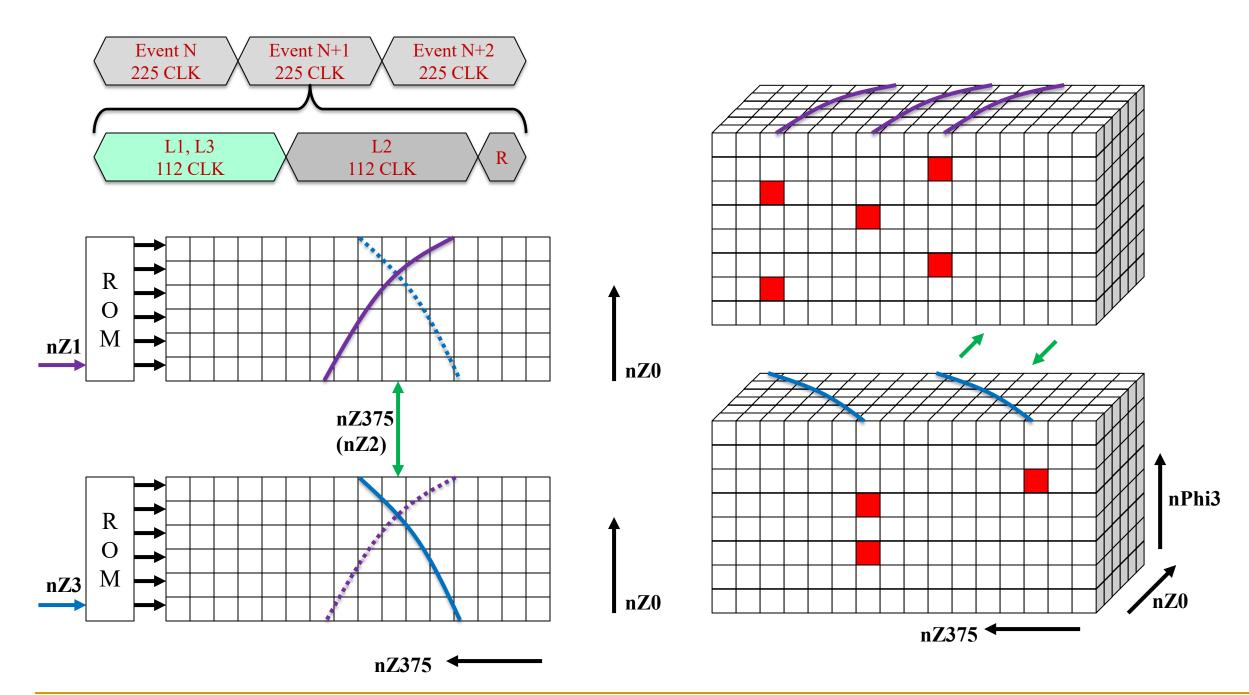

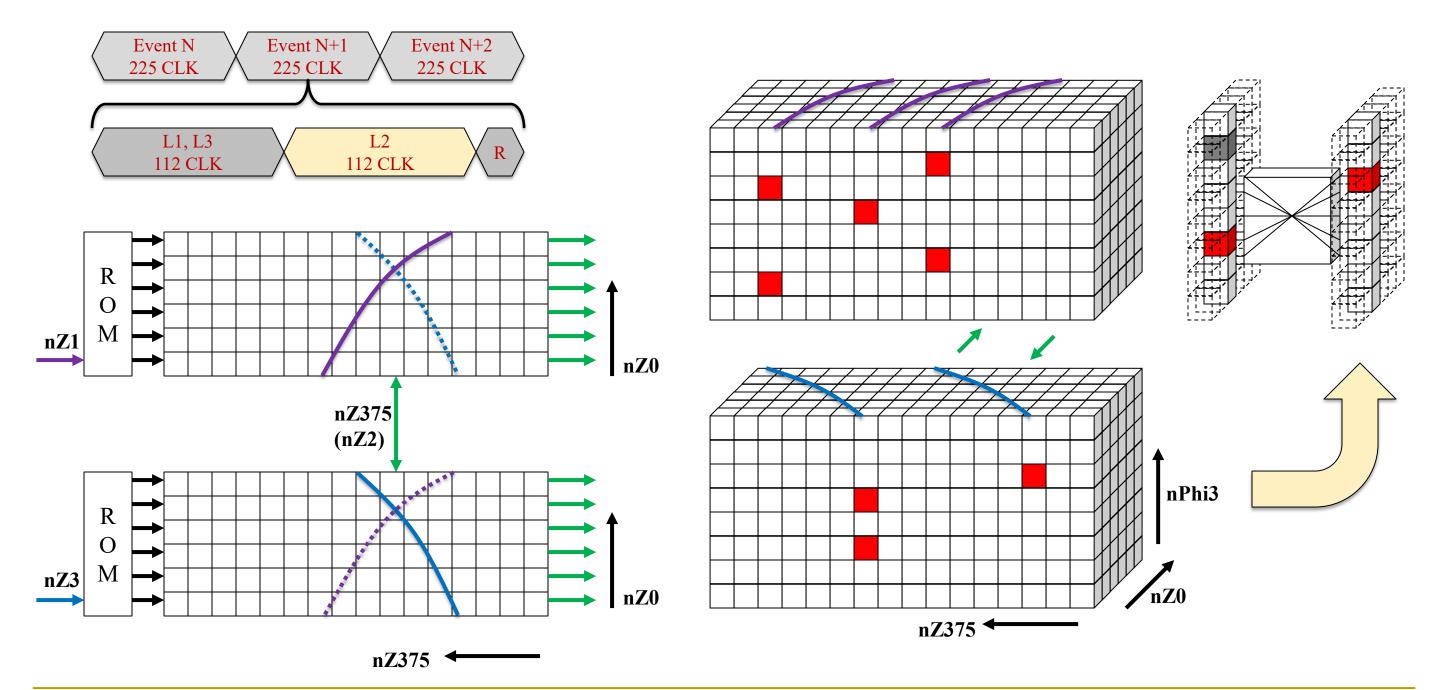

### System Division

Louise Skinnari et. al. 2020

System Division:

18 time slices

9 regions

Each TFP serves:

40 degrees.

25 ns x 18 = 450 ns

or 225 clock cycles

@500 MHz

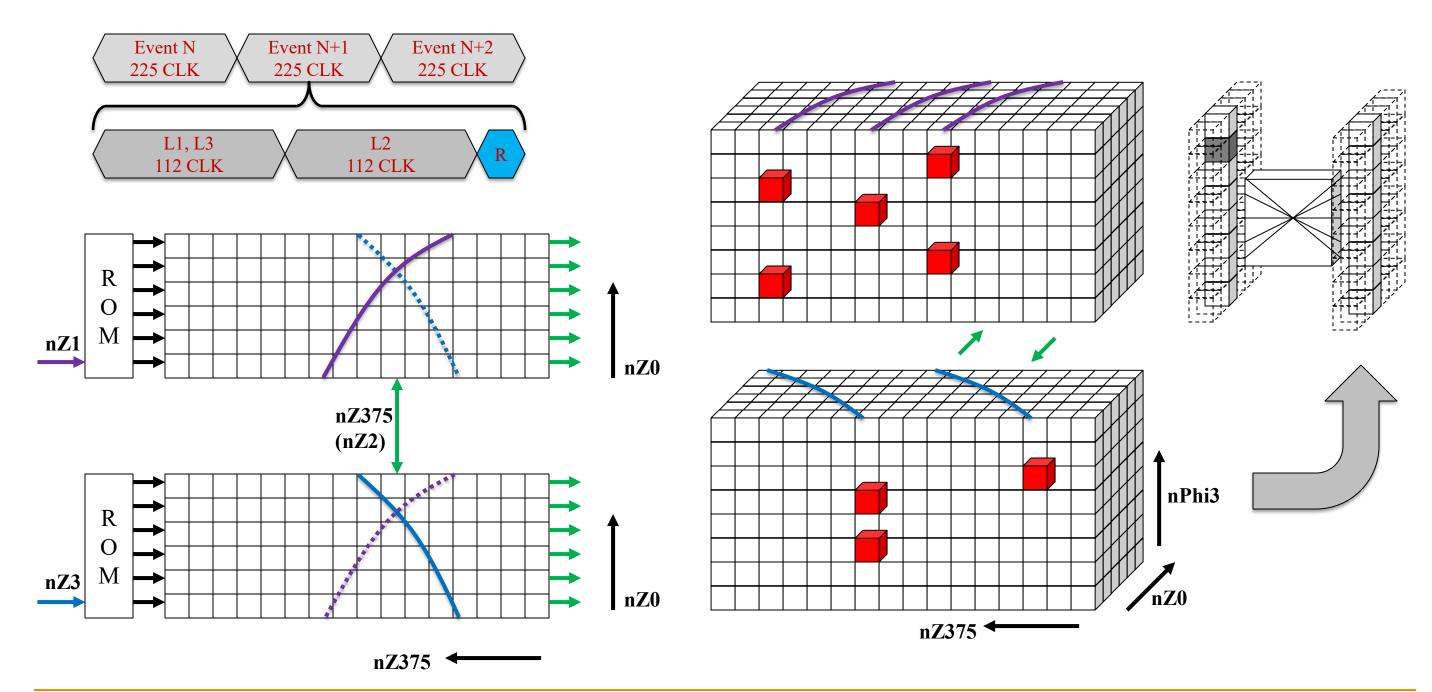

### Serving Range of Seeding Engine

- In each TFP, 4 seeding engines are implemented, each serving 2.4 m (full length) x 10 degrees plus overlap.

- Each engine sees <100 hits/layer per event.

- The layer 2 is divided with exact 10-degree boundaries.

- Overlapping in:

- Layer 1: +- 2.16 degrees, 14.3 degrees total

- Layer 3: +- 2.62 degrees, 15.2 degrees total

#### Generated Events: r-z View

- In 240 cm (z) x 10 degrees (phi) range, up to 112 hits per layer are generated, out of which, 10 are from good tracks.

- The z0 of the vertices spread in +- 10 cm along beam axis.

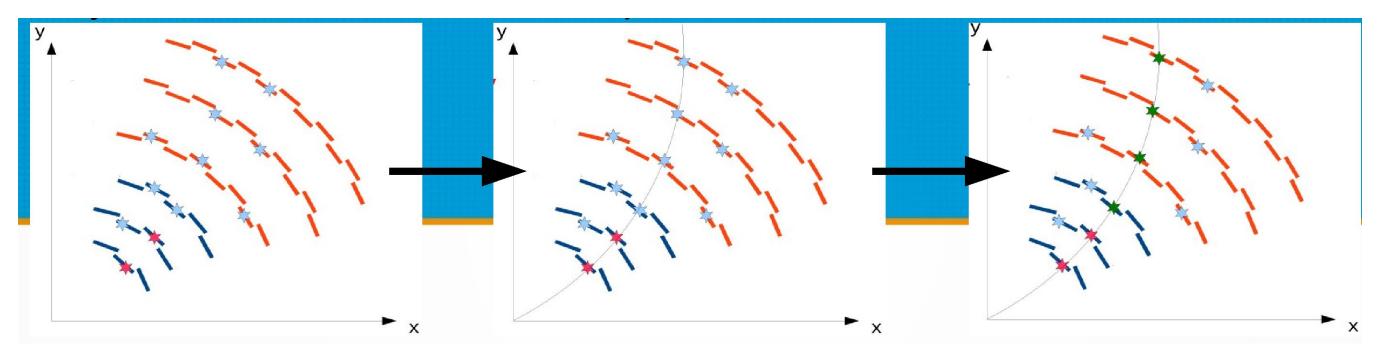

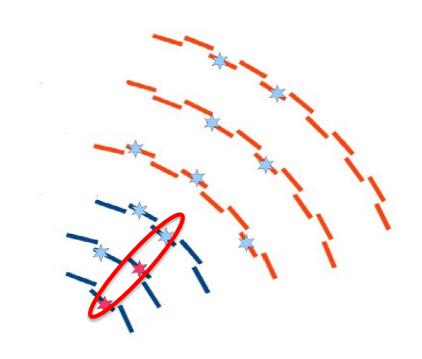

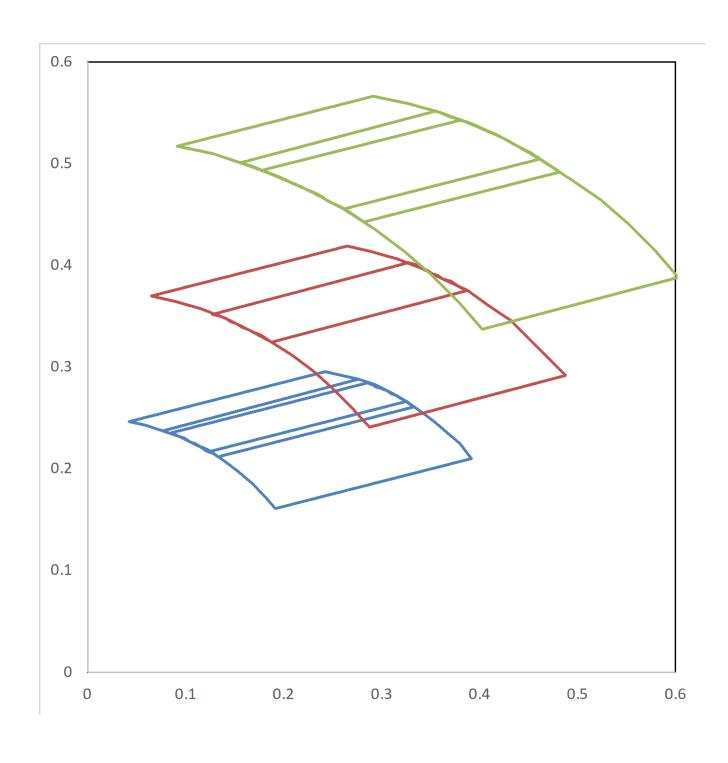

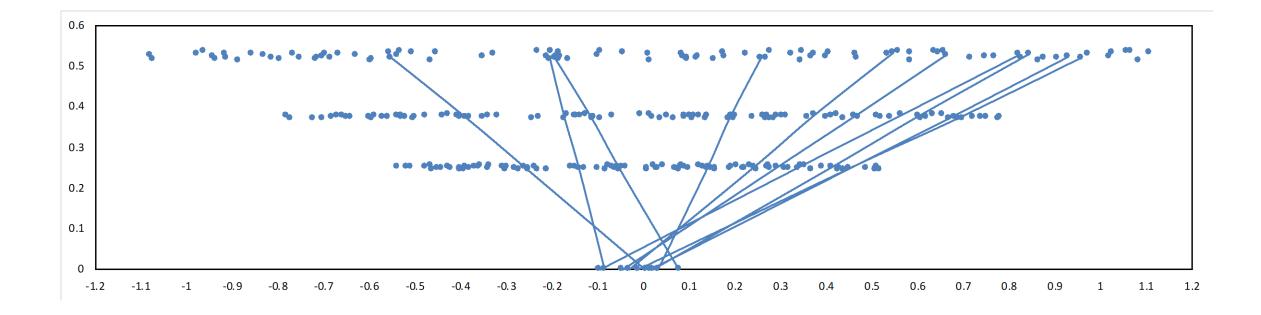

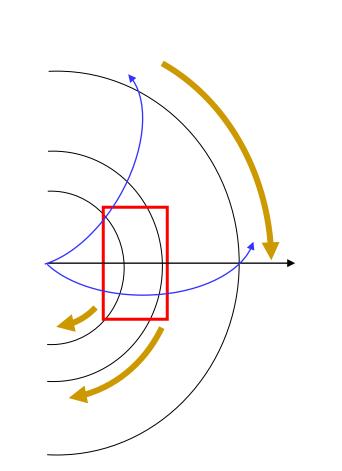

### The Events: r-phi View

- Minimum PT: 2GeV/c.

- The hits on Layer 2 is limited to 10 degrees, but hits on Layer 1 and 3 spread up to 16 degrees.

- The impact parameters of the tracks: +- 2 mm.

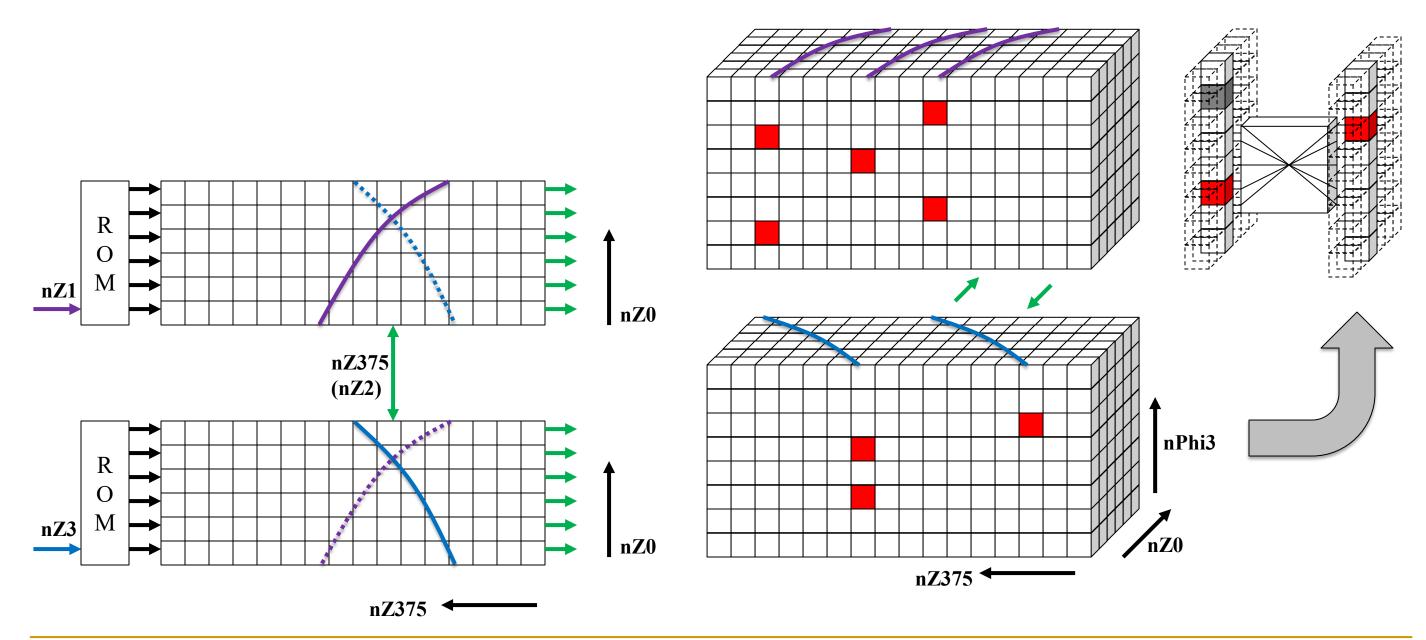

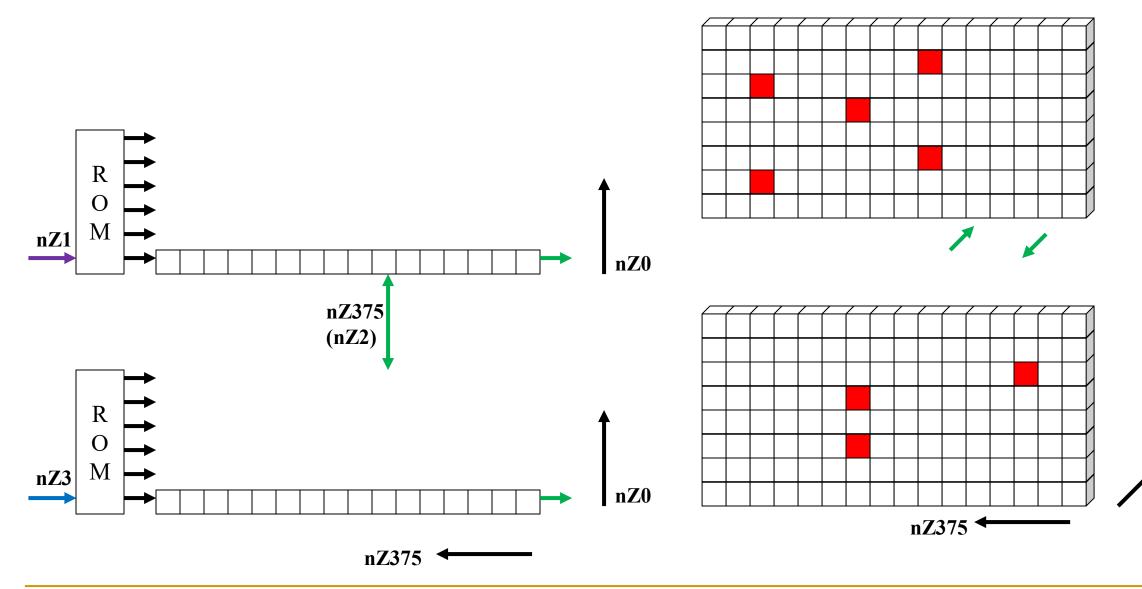

The 3D Seeding Engine for SP Layers

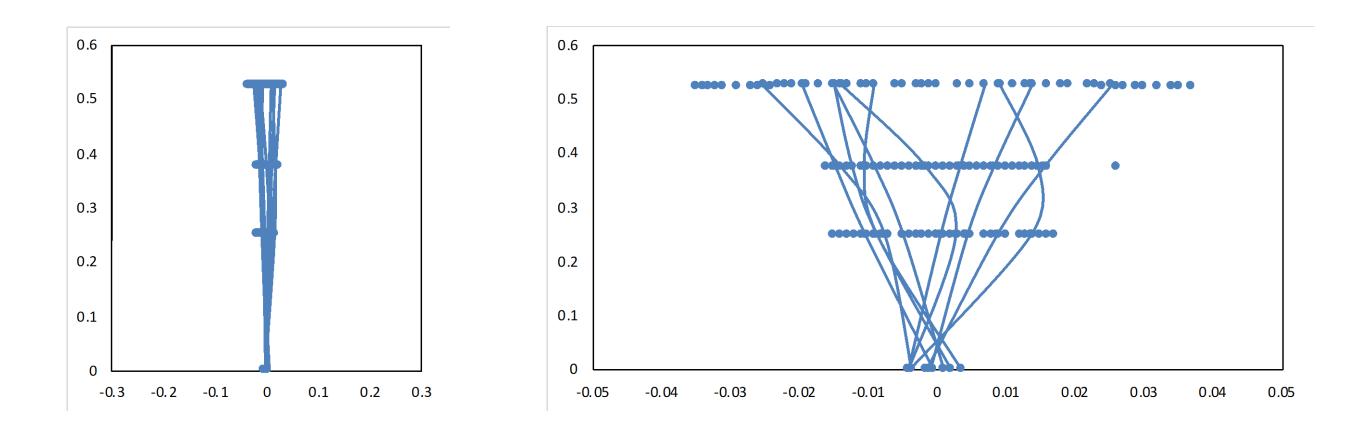

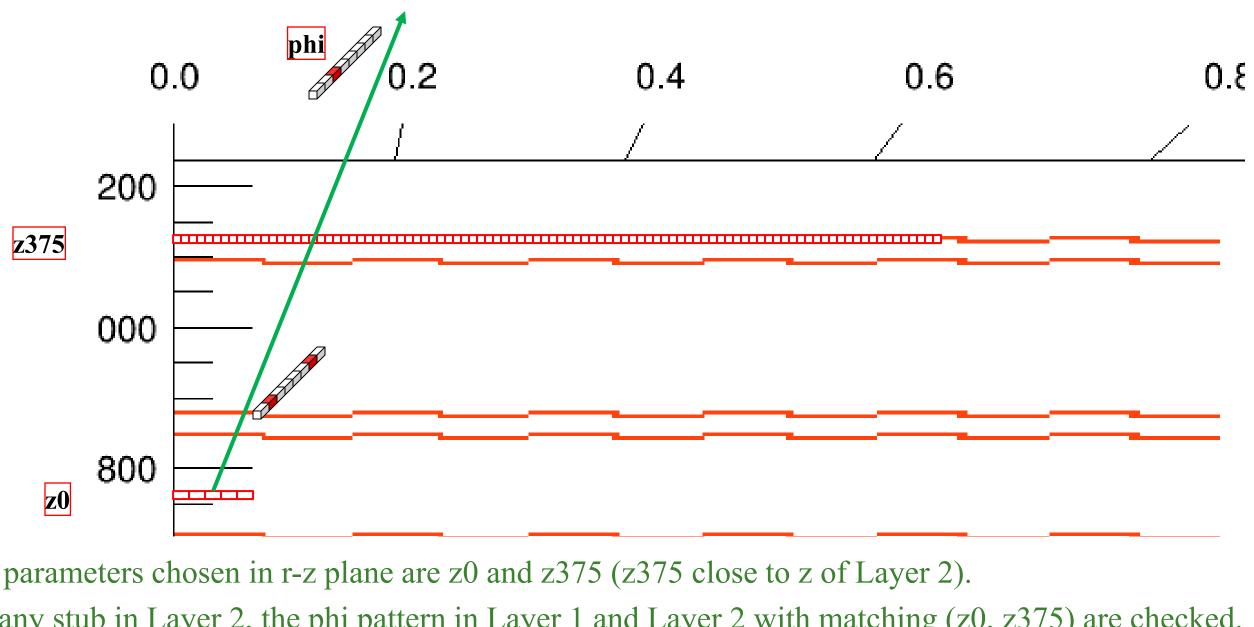

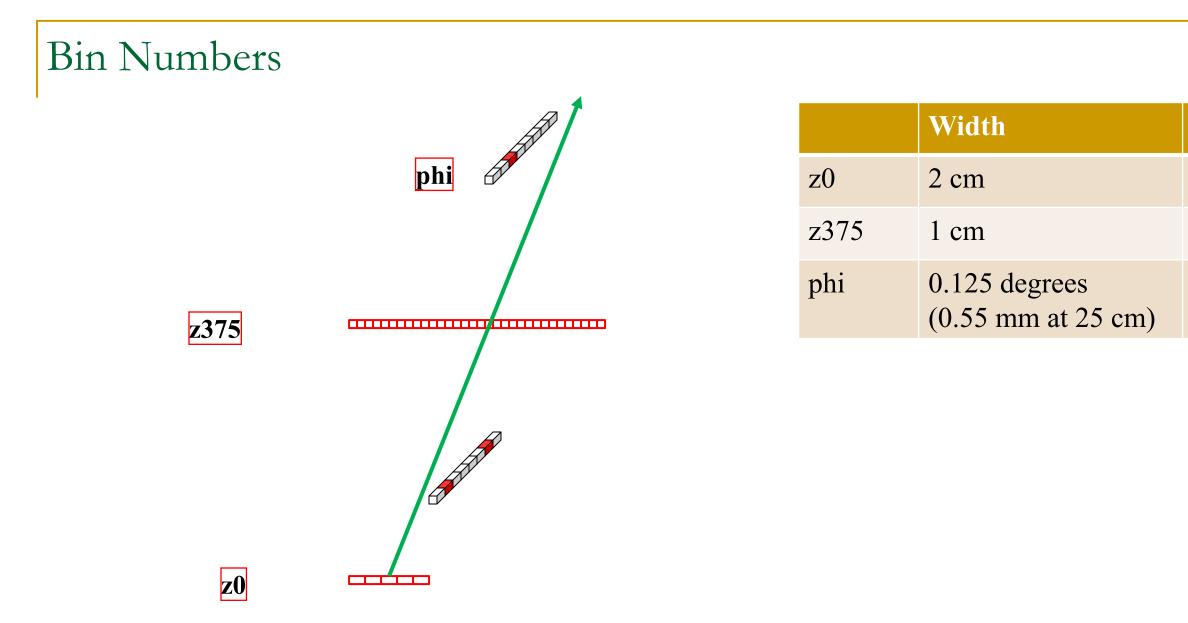

- The parameters chosen in r-z plane are z0 and z375 (z375 close to z of Layer 2).

- For any stub in Layer 2, the phi pattern in Layer 1 and Layer 2 with matching (z0, z375) are checked.

- The triplets matching not only in r-z, but also in r-phi are reported for further track fitting.

- Neither phi bins nor z bins can be too fine.

- Just checking r-phi or r-z would have too high fake rate.

- The 3-D track seeding (i.e., checking both r-phi and r-z) should provide sufficient fake stub rejection.

| Number               |

|----------------------|

| 10                   |

| 240                  |

| 128<br>(/16 degrees) |

# The Track Seeding Engine

Sept. 2021, Wu Jinyuan, Fermilab jywu168@fnal.gov

#### Structure of the Seeding Engine: Two RAM Banks

### Structure of the Seeding Engine: Single Physical RAM View

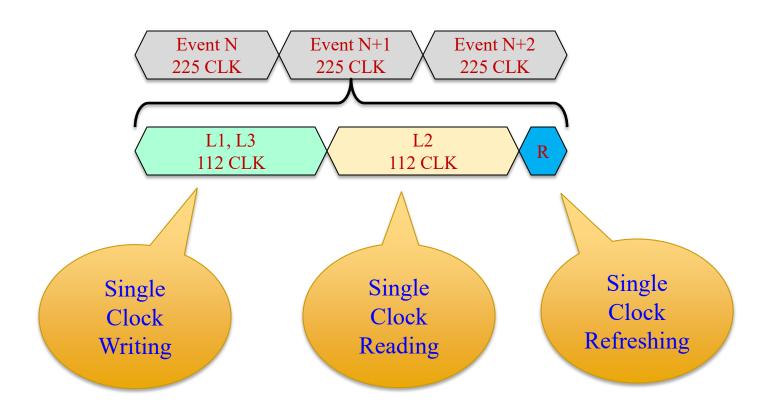

### General Timing

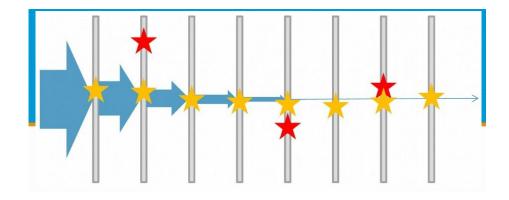

### Operation: (1) Filling Hits

### Operation: (2) Checking Coincidence

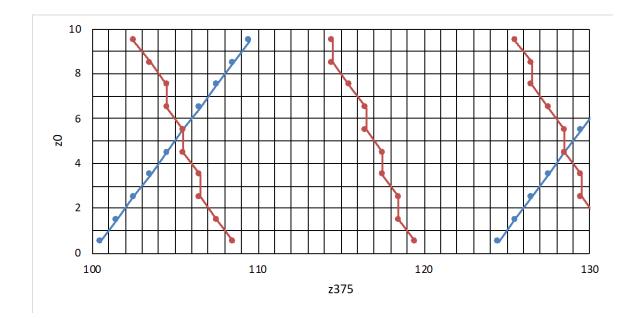

### Pattern Shifting and checking

- The bit patterns with the same z0 from Layer 1 and Layer 3 are shifted to align with the coincidence road array.

- The amount of shift is determined by phi2.

- Matching bits are output for further process.

### Operation: (3) Refresh Cycle

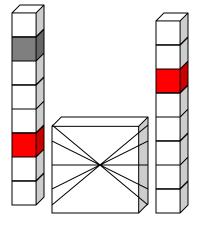

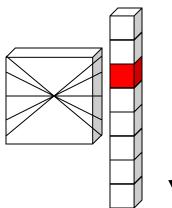

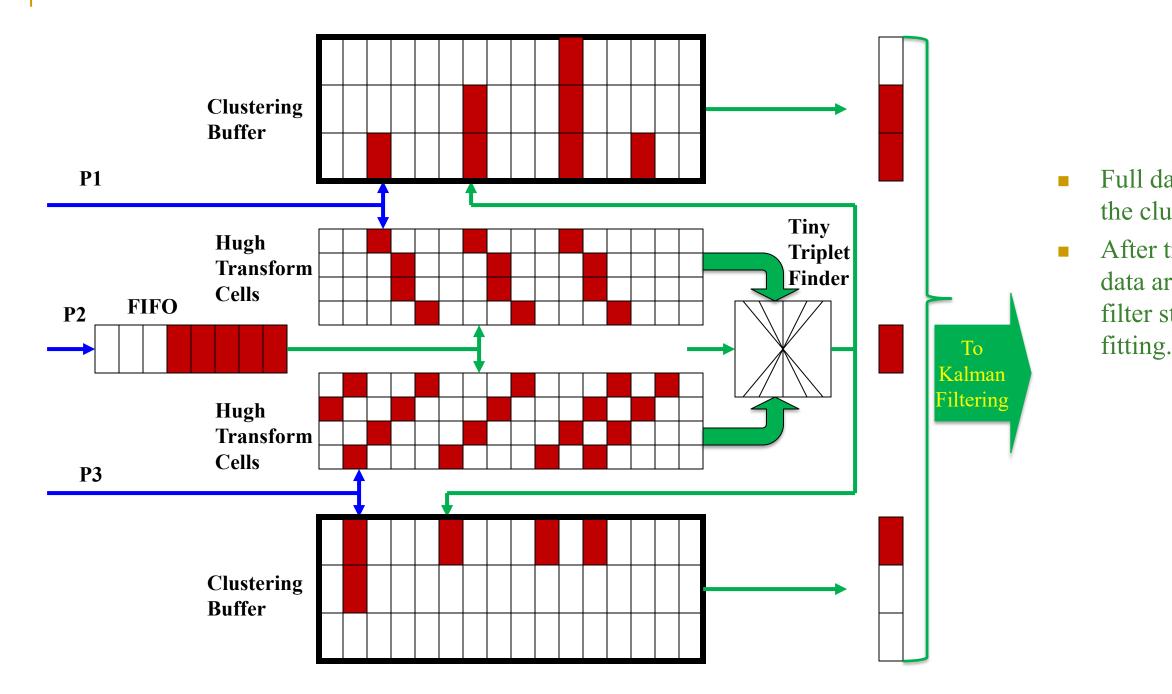

#### The Seeding Engine & Clustering Buffer

Full data of hits are stored in the clustering buffer.

After triplet finding, the full data are sent to the Kalman filter stage for further track

# Implementation in Cyclone 5 FPGA

Sept. 2021, Wu Jinyuan, Fermilab jywu168@fnal.gov

A 3D FPGA Track Segment Seeding Engine

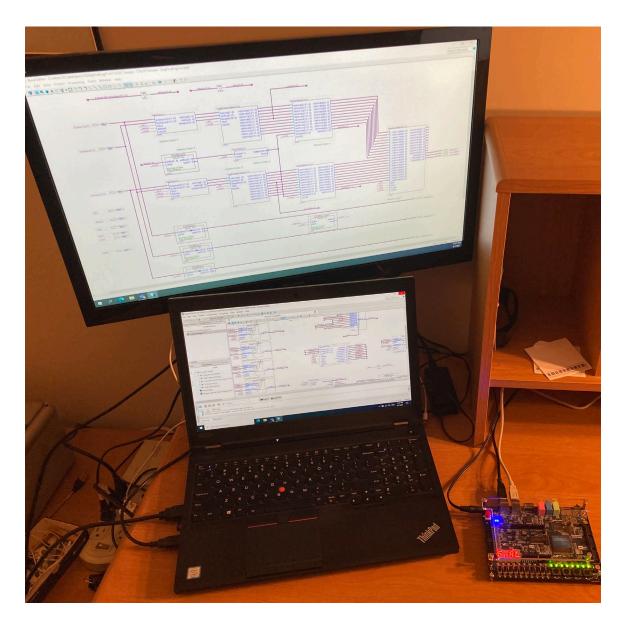

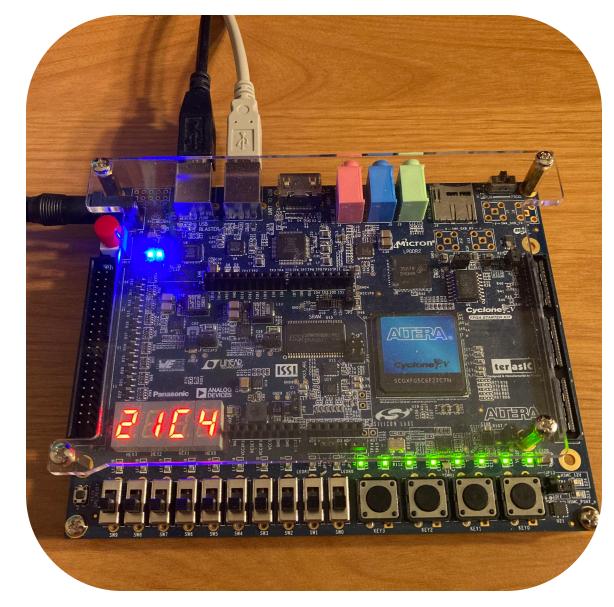

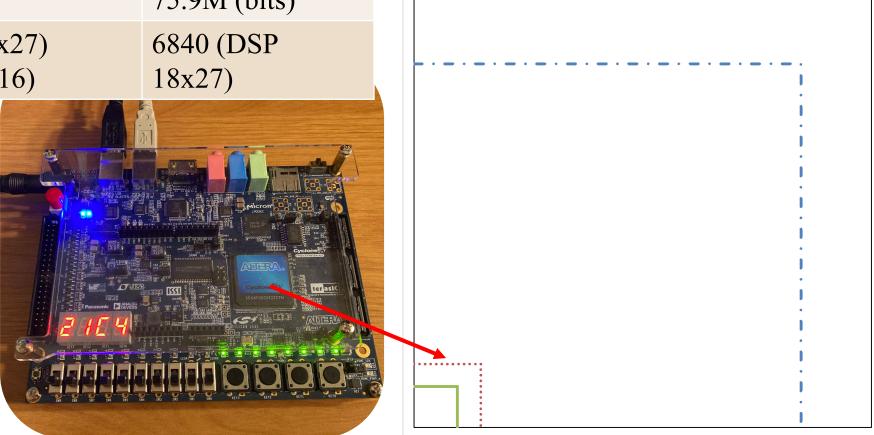

#### Home Test Stand and the Evaluation Module

- The seeding engine core firmware is implemented in Altera C5G evaluation module (179 USD ea.).

- The FPGA is Cyclone V GX 5CGXFC5C6F27C7N (171 USD ea.).

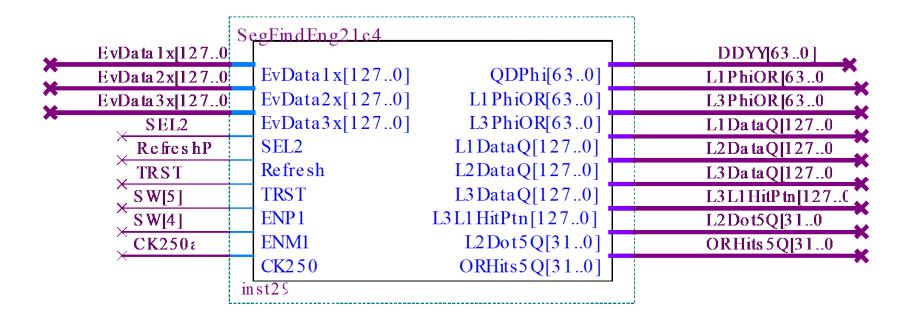

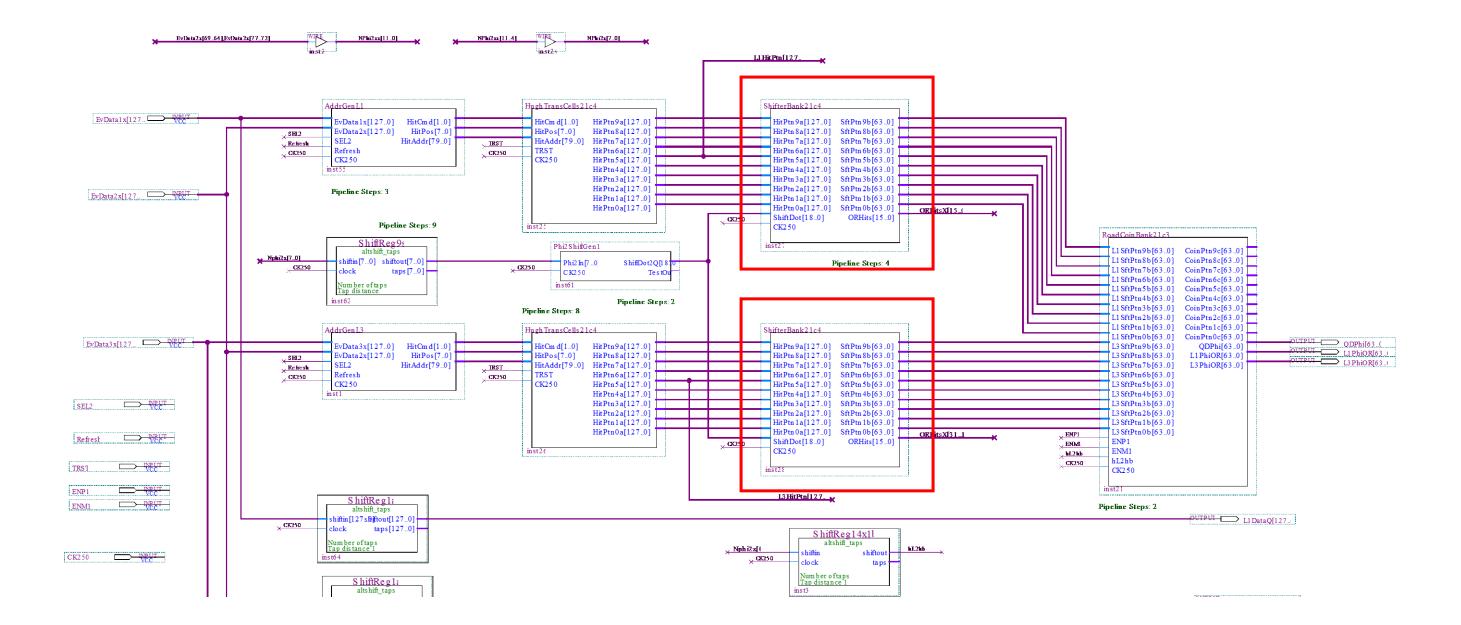

### The Seeding Engine Block I/O

- The hit data from Layer 1, 2 and 3 are fed into the engine, one hit per clock cycle.

- The primary coincidence outputs are in port DDYY[63..0] which represents up to 64 possible 1/PT values of the track segment.

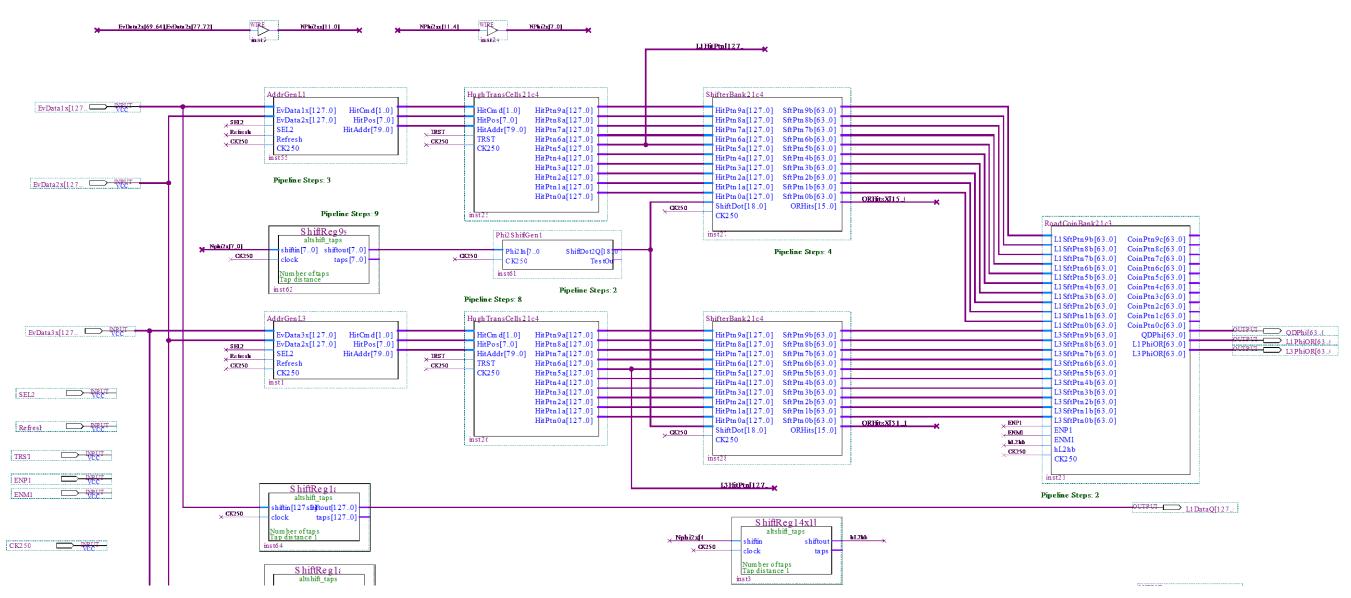

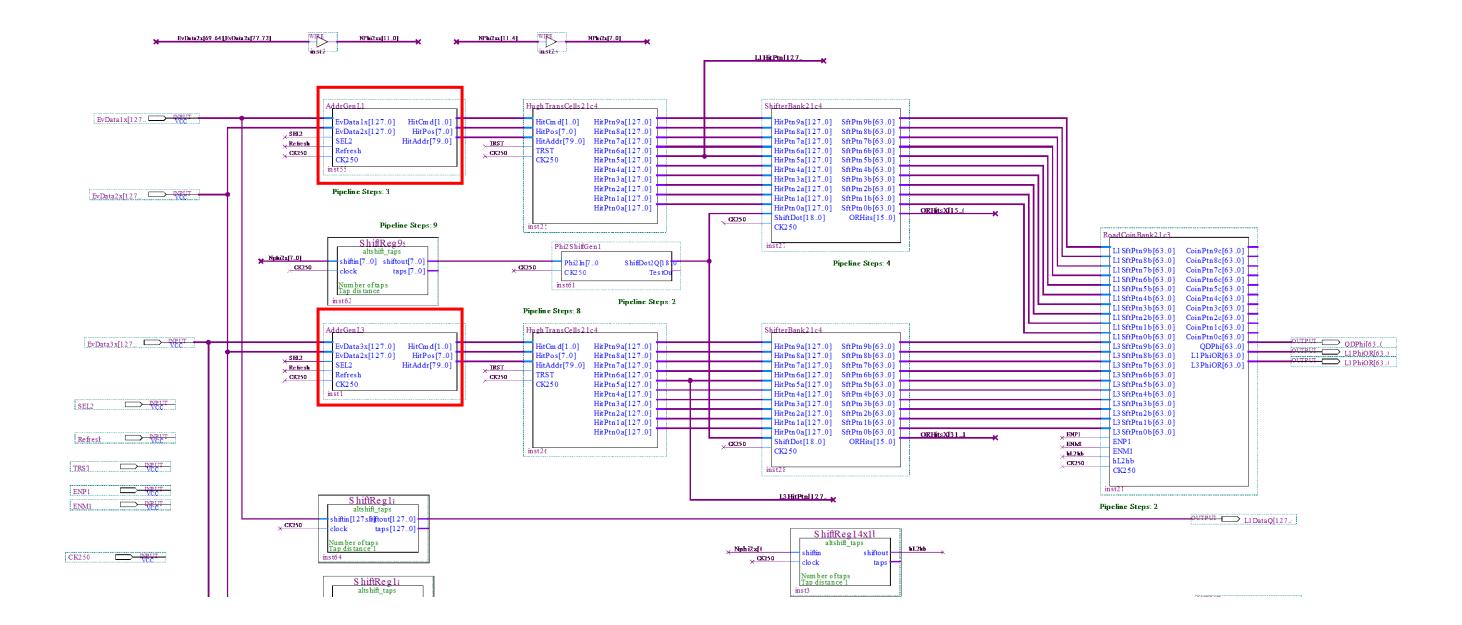

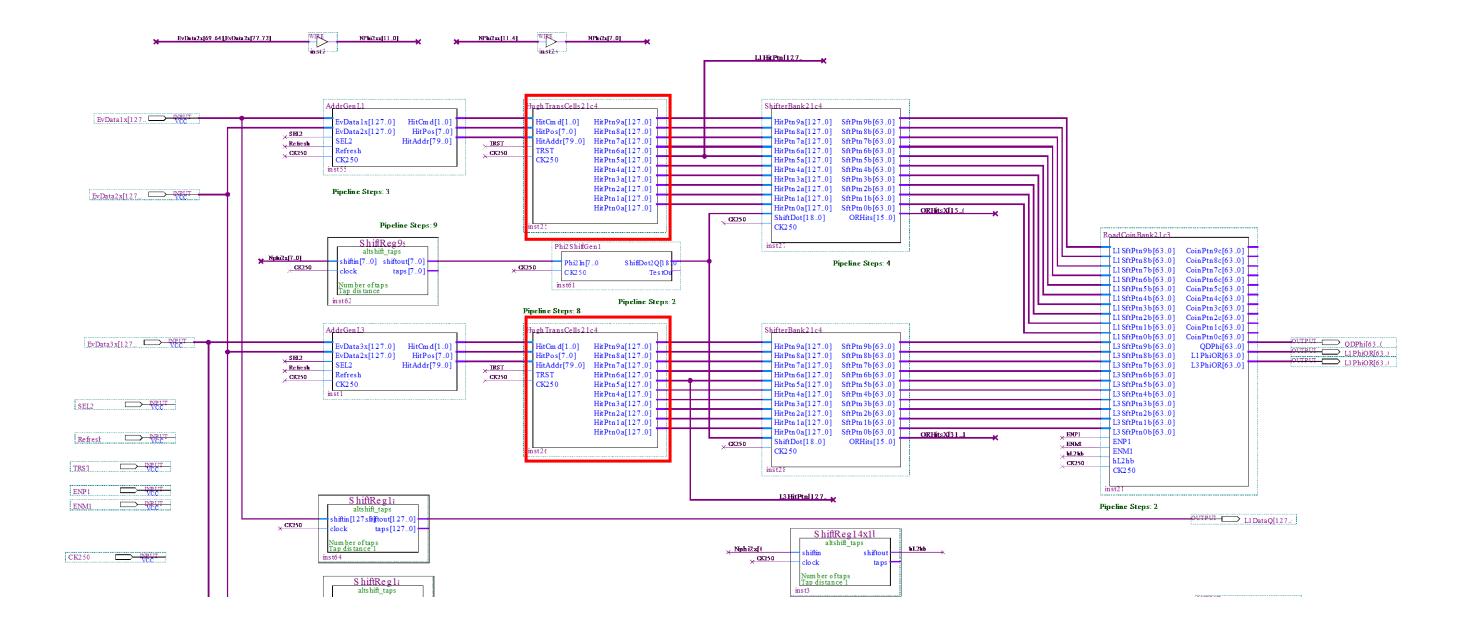

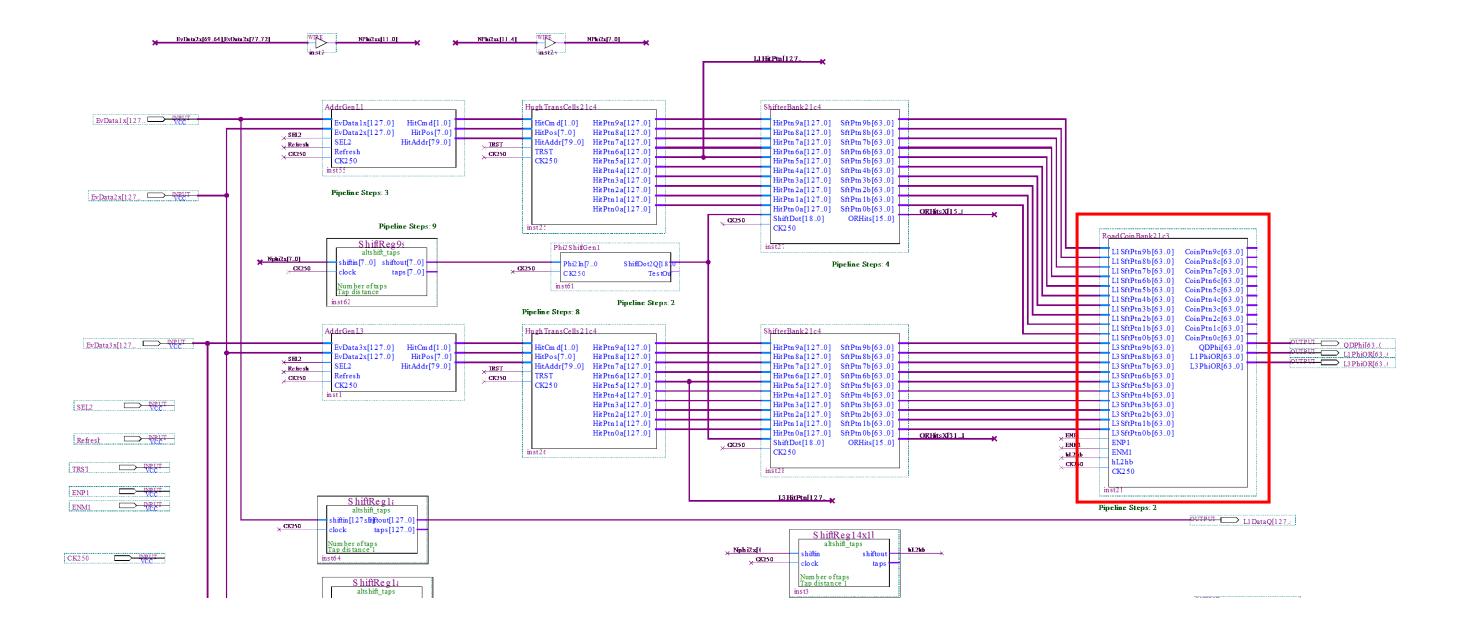

### Structure of the seeding engine

- The entire engine is organized as a pipeline so that it can run at high speed (250 MHz in Cyclone V).

- Blocks: Address Generation; Hugh Trans. Cells; Shifter Bank; Road Coincidence

### The Seeding Engine

| Address Conversion<br>Cells                                                                                                                                                                                                    | for Hugh Transform                                                                                                                                                | <pre>MemInit1.txt ~Format: Quartus .mif WIDTH=80;  DEPTH=256; ADDRESS_RADIX=HEX; DATA_RADIX=HEX; CONTENT BEGIN 00 : 00000000000000000000; 01 : 0000000000000000; 02 : 0000000000000000;</pre> | Format<br>WIDTH=80<br>DEPTH=25<br>ADDRESS_<br>DATA_RAD<br>CONTENT<br>00 : 222<br>01 : 232<br>02 : 232                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AddrGenL1         EvData1x[127.0]       HitCmd[         × SEL2       EvData2x[127.0]       HitPos         × Refresh       SEL2       HitAddr[7         × CK250       Refresh       CK250         Inst55       Pipeline Steps:3 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                             | 03       : 000000000000000000000000000000000000                                                                                                                                               | 03 : 242<br>04 : 252<br>05 : 252<br>06 : 262<br>07 : 272<br>08 : 282<br>09 : 282<br>00 : 292<br>0b : 262<br>0c : 262<br>0d : 262<br>0d : 262<br>0d : 262<br>0f : 262<br>10 : 262<br>11 : 262<br>13 : 263<br>14 : 303<br>15 : 313<br>16 : 323<br>17 : 323<br>18 : 333<br>19 : 343               |

| <ul> <li>have 10 RAM blocks z0.</li> <li>The z-coordinate z1 of for each z0 by checking</li> </ul>                                                                                                                             | 3 Hugh Transform Cells<br>corresponding 10 bins in<br>or z3 is converted to z375<br>ng the lookup table ROM.<br>epend on detector geometry<br>ng simulation data. | 1.5       : 000000000000000000000000000000000000                                                                                                                                              | 1a : 343         1b : 353         1c : 363         1d : 373         1e : 373         1f : 383         20 : 393         21 : 393         22 : 3a3         23 : 3b3         24 : 3c3         25 : 3c3         26 : 3d3         27 : 3e3         28 : 3e3         29 : 3f4         2b : 414         2c : 414         2c : 414         2d : 424         2e : 434         30 : 444         31 : 454 |

MemInit3.txt mat: Quartus .mif =80; =256; SS\_RADIX=HEX; RADIX=HEX; NT BEGIN 22222324242525262627; 23232424252526272728; 23242425262627272828; 24252526262727282929; 2525262627282829292a; 25262727282829292a2b; 2627272828292a2a2b2b; 27272829292a2a2b2b2c; 282829292a2a2b2c2c2d; 2829292a2b2b2c2c2d2d; 292a2a2b2b2c2c2d2e2e; 2a2a2b2b2c2d2d2e2e2f; 2a2b2c2c2d2d2e2e2f30; 2b2c2c2d2d2e2f2f3030; c2c2d2e2e2f2f303031; 2d2d2e2e2f2f30313132; 2d2e2e2f303031313232; 2e2f2f30303131323333; 2f2f3030313232333334; 2f303131323233333435; 30313132323334343535; 31313233333434353536; 32323333343435363637; 32333334353536363737; 33343435353636373838; 34343535363737383839; 3435363637373838393a; 35363637373839393a3a; 363637383839393a3a3b; 3737383839393a3b3b3c; 373838393a3a3b3b3c3c; 3839393a3a3b3b3c3d3d; 39393a3a3b3c3c3d3d3e; 393a3b3b3c3c3d3d3e3f; 3a3b3b3c3c3d3e3e3f3f; 3b3b3c3d3d3e3e3f3f40; 3c3c3d3d3e3e3f404041; c3d3d3e3f3f40404141; 3d3e3e3f3f4040414242; 3e3e3f3f404141424243; 3e3f4040414142424344; 3f404041414243434444; 40404142424343444445; 41414242434344454546; 41424243444445454646; 42434344444545464747; 43434444454646474748; 43444545464647474849; 44454546464748484949; 4545464747484849494a;

### The Seeding Engine

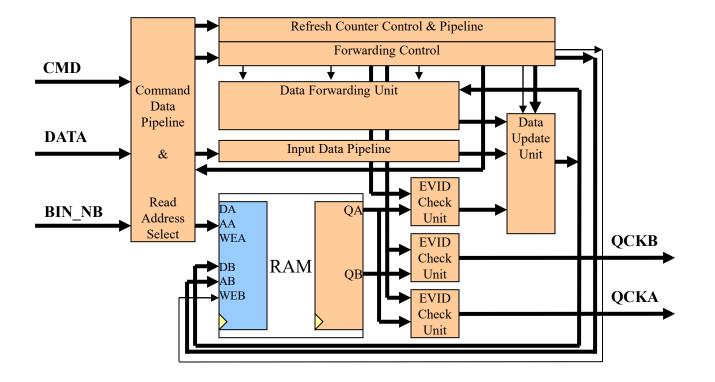

### Register-Like Block RAM for Hit Patterns

- The hit patterns are stored in the register-like BRAM.

- Each hit is processed in a single clock cycle.

- Single clock cycle refreshing allows fast preparation for next event.

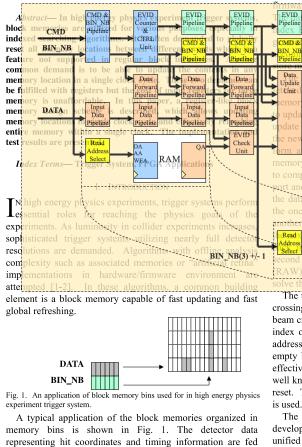

### **Register-Like Block RAM: Implementation**, Testing in FPGA and Applications for High **Energy Physics Trigger Systems**

Jinyuan Wu

Manuscript received May 20, 2016. This work was supported in part by Fermi Research Alliance, LLC under Contract No. DE-AC02-07CH11359 with the United States Department of Energy.

into the trigger system and in the processing stages of the

The author is with Fermi National Accelerator Laboratory, Batavia, IL 60510 USA (phone: 630-840-8911; fax: 630-840-2950; e-mail: jywu168@ fnal.gov).

| ware, the data are usually fetched one hit per clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| VIData are EVID stored EVID the block memory bins usi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ng an    |

| ex BIN NB as address, while the index can be eithe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | er the   |

| <mark>mæ</mark> ric coordinates or time stamp. In orde                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | r to     |

| with the second se | le to    |

| <del>e mu</del> ltiple hits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| date memory block bins are to be updated as the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| <b>hit</b> d in every clock cycle. While writing a data i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| nory within one clock is straightforward, the challer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <u> </u> |

| pdate the memory location within a single clock cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| ate a memory bin, the contents of the bin are first rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 out,   |

| new hit data is concatenated <b>FVID</b> Check tiQCKBdata we                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ord to   |

| n a new wata word which is ther <u>Unit</u> ritten back int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | o the    |

| nory bin. WFFne RAM ng process takes several clock c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| omplete Which requires a dual port memory with a re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| t and a writing port and a suitably designed pipeline s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| data can be processed one hit per clock cycle. Not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| once a hit to be filled into a bin is fed into the pip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| ther hit to be filled into the name tever an come as ea<br>eadyl cycl ba in this case. the time tever a cheek the tever w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | rly as   |

| ead t cycle in this case, the first (Check as not been w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ritten   |

| tress to weather RAM pin before the locating cycle of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | f the    |

| ond update process. This is similar as the read-after                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| W) haza <mark>rd in contempora</mark> ry microprocessor design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10       |

| e this hazard, a data forwarding scheme is utilized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

The trigger firmware processes data belonging to one beam crossing. After filling up the memory with the data from a beam crossing, the algorithm will search the data based on the index of the bins. Note that the searching process may not address all bins containing the hit data and it may also address empty bins. After reading process, all memory bins will be effectively cleared to prepare for the next beam crossing. It is well known that regular block memories do not support global reset. To fulfill this requirement, an event ID tagging scheme

The single clock updating and global refreshing schemes developed in our previous work [3] are combined into a unified scheme in this work. In this paper, global refreshing scheme is first discussed in Section II, followed by the pipeline structure with data forwarding support in Section III. The implementation and test results of the entire scheme are presented in Section IV.

II. GLOBAL REFRESH SCHEME FOR BLOCK MEMORY Intrinsically, the block memories can only be accessed one

### The Seeding Engine

### Shifters

| HughTransCells21 | c4             |         | S  | hifterBank21c4 |               |    |            |

|------------------|----------------|---------|----|----------------|---------------|----|------------|

| HitCmd[10]       | HitPtn9a[1270] |         |    | HitPtn9a[1270] | SftPtn9b[630] |    |            |

| HitPos[70]       | HitPtn8a[1270] |         |    | HitPtn8a[1270] | SftPtn8b[630] |    |            |

| HitAddr[790]     | HitPtn7a[1270] |         |    | HitPtn7a[1270] | SftPtn7b[630] |    |            |

| TRST             | HitPtn6a[1270] |         |    | HitPtn6a[1270] | SftPtn6b[630] |    |            |

| CK250            | HitPtn5a[1270] |         |    | HitPtn5a[1270] | SftPtn5b[630] |    |            |

|                  | HitPtn4a[1270] |         |    | HitPtn4a[1270] | SftPtn4b[630] |    |            |

|                  | HitPtn3a[1270] |         |    | HitPtn3a[1270] | SftPtn3b[630] |    |            |

|                  | HitPtn2a[1270] |         |    | HitPtn2a[1270] | SftPtn2b[630] |    |            |

|                  | HitPtn1a[1270] |         |    | HitPtn1a[1270] | SftPtn1b[630] |    |            |

|                  | HitPtn0a[1270] |         |    | HitPtn0a[1270] | SftPtn0b[630] | OR | Hits XI1 : |

|                  |                | V CK250 |    | ShiftDot[180]  | ORHits[150]   |    |            |

| inst2:           |                | ×       |    | CK250          |               |    |            |

|                  |                |         |    |                |               |    |            |

| Phi2ShiftG       | en1            |         | iı | list27         |               |    |            |

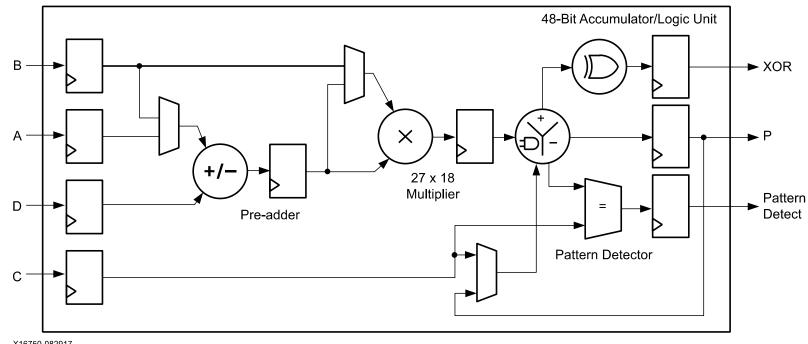

The multipliers in FPGA DSPs are used to implement shifters.

X16750-082917

### The Seeding Engine

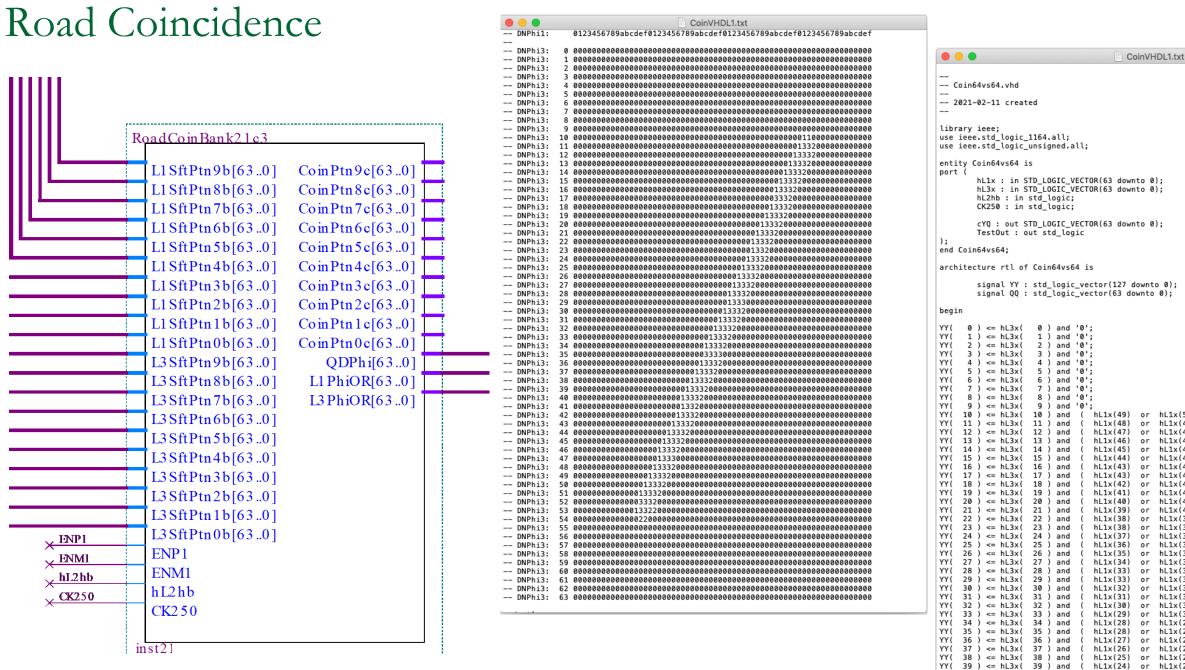

- Shifted bit patterns are checked by coincidence road array.

- The r-phi logic equations are generated with simulation.

40) <= hL3x(

41 ) <= hL3x(

42 ) <= hL3x(

45 ) <= hL3x(

44 ) <= hL3x( 44 ) and

- 6132

43 ) <= hL3x(

40 ) and

41 ) and

42 ) and

43 ) and

45 ) and

hL1x(23)

hL1x(23)

hL1x(22)

hL1x(21)

hL1x(20)

hL1x(19)

|   | or | hL1x(50) | ); |          |    |           |    |   |

|---|----|----------|----|----------|----|-----------|----|---|

|   | or | hL1x(49) | or | hL1x(50) | ); |           |    |   |

|   | or | hL1x(48) | or | hL1x(49) | or | hL1x(50)  | ); |   |

|   | or | hL1x(47) | or | hL1x(48) | or | hL1x(49)  | ); |   |

|   | or | hL1x(46) | or | hL1x(47) | or | hL1x(48)  | ); |   |

|   | or | hL1x(45) | or | hL1x(46) | or | hL1x(47)  | ); |   |

|   | or | hL1x(44) | or | hL1x(45) | or | hL1x(46)  | ); |   |

|   | or | hL1x(44) | or | hL1x(45) | ); |           |    |   |

|   | or | hL1x(43) | or | hL1x(44) | or | hL1x(45)  | ); |   |

|   | or | hL1x(42) | or | hL1x(43) | or | hL1x(44)  | ); |   |

|   | or | hL1x(41) | or | hL1x(42) | or | hL1x(43)  | ); |   |

|   | or | hL1x(40) | or | hL1x(41) | or | hL1x(42)  | ); |   |

|   | or | hL1x(39) | or | hL1x(40) | or | hL1x(41)  | ); |   |

|   | or | hL1x(39) | or | hL1x(40) | ); |           |    |   |

|   | or | hL1x(38) | or | hL1x(39) | or | hL1x(40)  | ); |   |

|   | or | hL1x(37) | or | hL1x(38) | or | hL1x(39)  | ); |   |

|   | or | hL1x(36) | or | hL1x(37) | or | hL1x(38)  | ); |   |

|   | or | hL1x(35) | or | hL1x(36) | or | hL1x(37)  | ); |   |

|   | or | hL1x(34) | or | hL1x(35) | or | hL1x(36)  | ); |   |

|   | or | hL1x(34) | or | hL1x(35) | or | hL1x(36)  | ); |   |

|   | or | hL1x(33) | or | hL1x(34) | or | hL1x(35)  | ); |   |

|   | or | hL1x(32) | or | hL1x(33) | or | hL1x(34)  | ); |   |

|   | or | hL1x(31) | or | hL1x(32) | or | hL1x(33)  | ); |   |

|   | or | hL1x(30) | or | hL1x(31) | or | hL1x(32)  | ); |   |

|   | or | hL1x(29) | or | hL1x(30) | or | hL1x(31)  | ); |   |

|   | or | hL1x(29) | or | hL1x(30) | or | hL1x(31)  | ); |   |

|   | or | hL1x(28) | or | hL1x(29) | or | hL1x(30)  | ); |   |

|   | or | hL1x(27) | or | hL1x(28) | or | hL1x(29)  | ); |   |

|   | or | hL1x(26) | or | hL1x(27) | or | hL1x(28)  | ); |   |

|   | or | hL1x(25) | or | hL1x(26) | or | hL1x(27)  | ); |   |

|   | or | hL1x(24) | or | hL1x(25) | or | hL1x(26)  | ); |   |

|   | or | hL1x(24) | or | hL1x(25) | ); |           |    |   |

|   | or | hL1x(23) | or | hL1x(24) | or | hL1x(25)  | ); |   |

|   | or | hL1x(22) | or | hL1x(23) | or | hL1x(24)  | ); |   |

|   | or | hL1x(21) | or | hL1x(22) | or | hL1x(23)  | ); |   |

|   | or | hL1x(20) | or | hL1x(21) | or | hL1x(22)  | ); |   |

| _ | or | h11v/10) | or | h11v(20) | or | hl 1v(21) | ١. | _ |

# **Test Results**

### Raw Input Data and Output Data

🛑 😑 📄 HitD... — Edited 🗸 00L1PXFMkP`PV] 00L1PXFN8m^4V^ 00L1PXF0[nkLV 00L1PPaaaaaWP 00L1PPaaaaaaWQ 00L1PP@@@@@WR 00L1PP@@@@@WS 00L1PP@@@@@WT 00L1PPaaaaaWU 00L1PP@@@@@WV 00L1PPaaaaaaWW 00L1PP@@@@@WX 00L1PPaaaaaaWY 00L1PPaaaaaWZ 00L1PP@@@@@@W[ 00L1PPaaaaaaW 00L1PP@@@@@@W] 00L1PPaaaaaaW^ 00L1PP@@@@@@W 00L2PY@@L@^VPP 00L2PY@AT0gJPQ 00L2PY@B[UMXPR 00L2PY@CaL[UPS 00L2PY@D\l1MPT 00L2PY@EaD\hPU 00L2PY@F0ZM9PV 00L2PY@GYH3iPW 00L2PY@HU8jHPX 00L2PY@IN:V:PY 00L2PX@JjjU`PZ 00L2PX@K0W0KP[

- Hits (stubs) are sent into the seeding engine.

- Each line is a hit in a detector layer.

- Typical data: 100 hits/layer with 10 good tracks with 90 random hits.

- The seeding engine outputs a 64-bit pattern, and the non-zero bits represent a potential track segment.

000000200000000040405950324C38 000000000000400041405950324C38 000001000000000042405950324C38 000000000001000043405950324C38 000000004000000044405950324C38 000000000000800045405950324C38 000020000000800046405950324C38 000000000000800047405950324C38 000000020000000048405950324C38 000400000000000049405950324C38 000000000000000004A405850324C38 0000000001000004B405850324C38 00000000000000004C405850324C38 00000000000000004D405850324C38 0000000000000004E405850324C38 0000000008000004F405850324C38 000000000000000040415850324C38 000000000000000041415850324C38 000020000000000042415850324C38 0000000020000043415850324C38 00000000000000044415850324C38 000000000000000045415850324C38 00000000000000046415850324C38 000000000000000047415850324C38

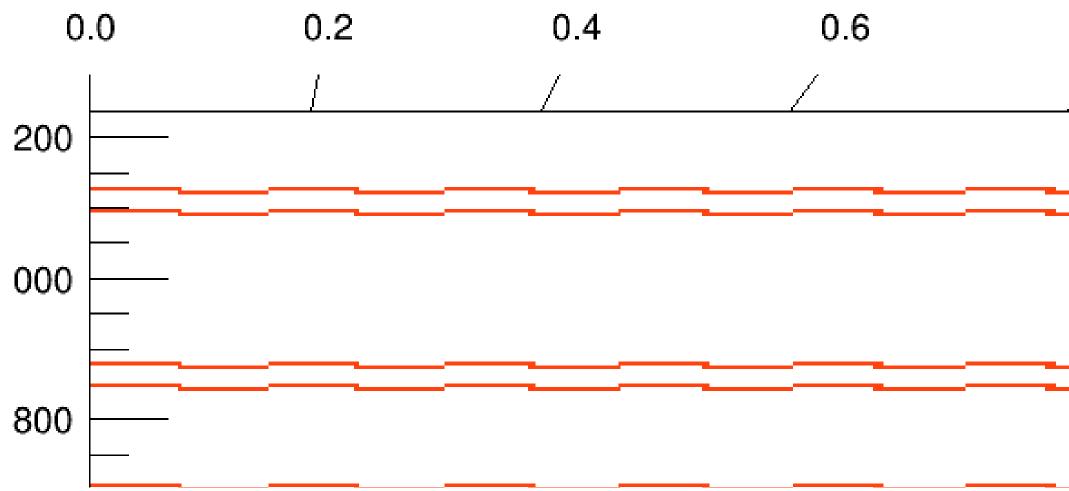

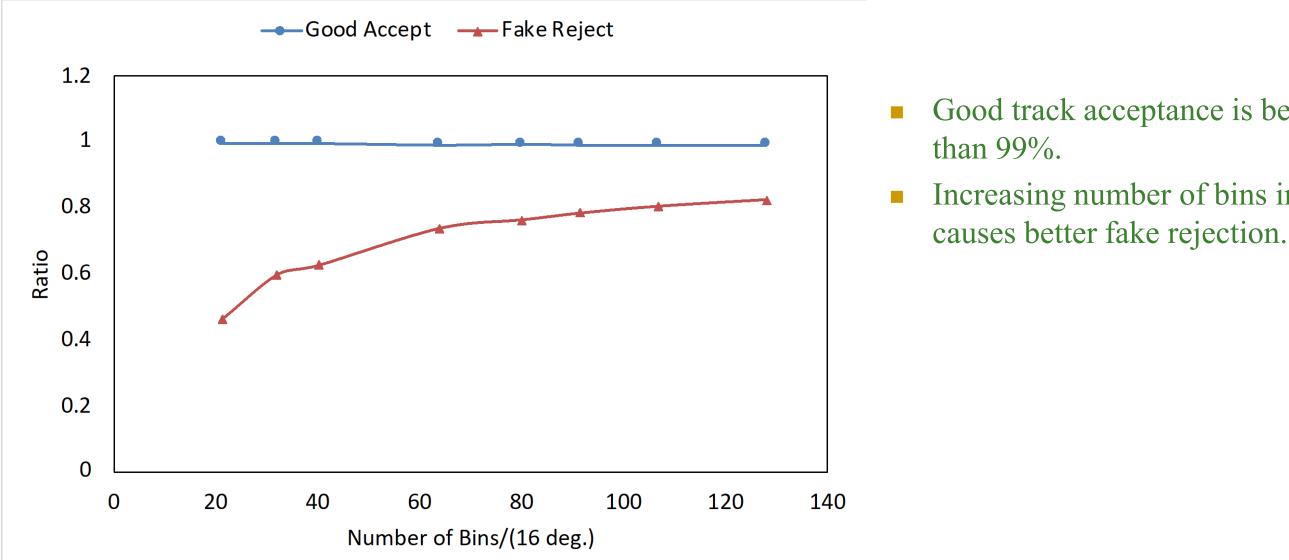

### Good Track Acceptance and Fake Rejection

### Good track acceptance is better

Increasing number of bins in phi

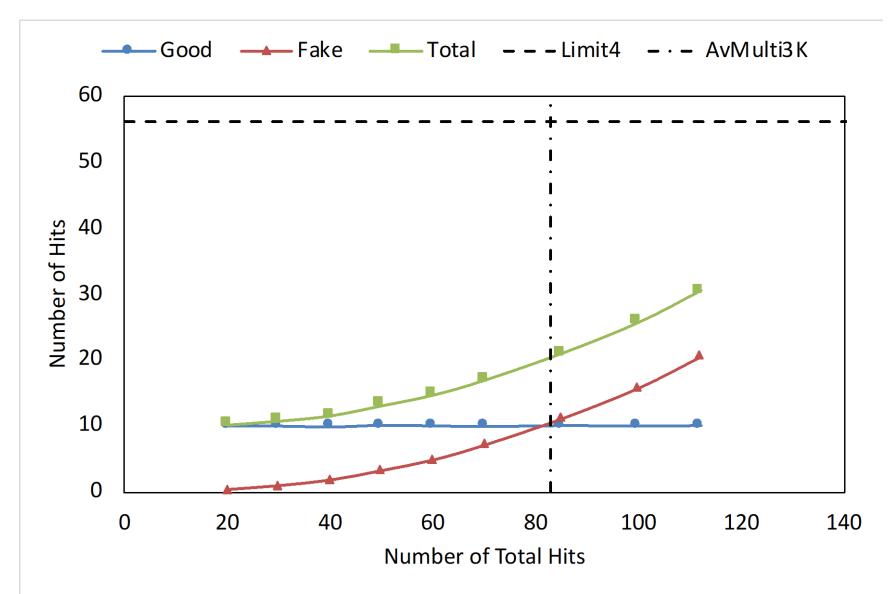

### Fake Tracks due to High Occupancy

- When number of total hits per event (BX) is low, fake rate is low.

- Event beyond occupancy of 3000 stubs/layer for the whole detector (the AvMulti3K line), total number of coincidence is still manageable.

- The dash line Limit4 indicate total coincidence allowed in fitting stage if each coincidence is processed with 4 clock cycles.

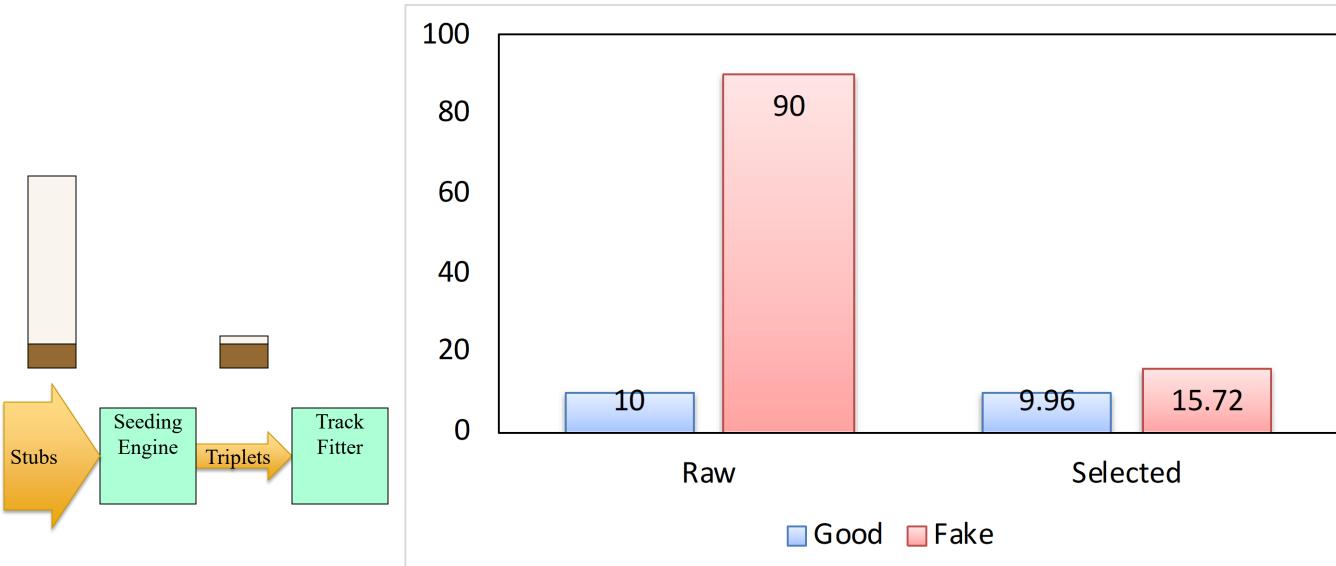

### Performance of the Seeding Engine

- Most of fake hits are rejected while good tracks are preserved.

- Data volume sent to the fitting stage is much smaller.

### Resource Usage:

|                | Used in a                     | Available in    | Available in     |

|----------------|-------------------------------|-----------------|------------------|

|                | Seeding Engine                | Cyclone 5       | Ultra-scale Plus |

|                | core                          | 5CGXFC5C6F27C7N | VU9P             |

| Logic<br>Cells | 12446 (ALM)<br>Eq. 32.9K (LC) | 29080 (ALM)     | 2586K (LC)       |

| Block          | 150 (M10K)                    | 446 (M10K)      | 75.9M (bits)     |

| RAM            | 743K (bits)                   | 4567K (bits)    |                  |

| DSP            | 100 (16x16                    | 150 (DSP 27x27) | 6840 (DSP        |

|                | Multipliers)                  | Eq. 300 (16x16) | 18x27)           |

- The seeding engine core fits the Cyclone 5 device with  $\sim$ 45% resource usage.

- Four cores are needed in VU9P and it looks possible.

### - VU9P ..... 5CGXFC5C6F27C7N \_\_\_\_ Seeding Engine 21c4

# Summary

- Algorithms: wellknown in the field.

- □ The fake rate of track segment seeding with triplets is lower.

- Implementations: exist in the field.

- □ The challenge is how to fit into a reasonable sized FPGA.

- Methods of solving the implementation challenge: this work.

- Using Tiny Triplet Finder so that only a small number of coincidence roads (product terms) are implemented.

- □ Hit patterns are implemented with "registerlike RAM" which allows single clock update, read and refresh operations.

- Lookup tables and coincidence roads are auto initiated using simulation data to accommodate detector geometry or alignment variations.

# Introduction

- For high-luminosity operation, 3D track segment seeding becomes necessary:

- Usable bin sizes in z or phi direction can't be too fine due to:

- Multiple scattering

- Non-zero impact parameter

- The 2D segment seeding would yield too many fake segments.

- Constraints in both r-z and r-phi planes help to reduce fake segments.

- Using the Tiny Triplet Finder to implement 3D track segment seeding engines

- The Tiny Triplet Finder is a low-resource usage scheme for track segment finding in FPGA.

- It becomes affordable to implement 3D seeding engines since the resource usage is low.

- A true 3D track segment seeding engine has been implemented and tested.

- Detector partition, data timing etc. are based on the seeding-fitting approach in recent CMS presentations: [Mark Pesaresi, ACES 2020] and [Luigi Calligaris RT2020].

- Stubs are generated on idealized Outer Tracker 3 PS layers.

- Operates as intended.

triplets of stubs becomes necessary.

Wu et. al. 2004 https://indico.cern.ch/event/418639/contributions/1018451 /attachments/868833/1216631/lowpt\_lecc2004p.pdf

"stub  $1 \div 4 mm$ ≤ 100 µm

### If the separation of silicon sensor layers were large ( $\sim 10 \text{ mm}$ ), then stub pairing would be sufficient.

# Given the separation of $\sim 4 \text{ mm in}$ PS and 2S module, correlating

- At 200 pile-up, the tracker sees 15k-20k stubs = > ~ 3000 stubs/layer.

- There are  $\sim 300$  high Pt tracks (Pt > 2 GeV).

- About 90% stubs are not associated with any high Pt track. => more than 90% stub pairs are fake.

- Requesting additional constraints from 3 or more stubs (triplet) will pre-exclude fake pairs.

### The Searching Range: Layer 2 to 1 and 3

| PT(GeV/c)                        | 2.000    |         |         |

|----------------------------------|----------|---------|---------|

| В(Т)                             | 4.000    |         |         |

| RO(m)                            | 1.667    |         |         |

| Z0(m)                            | 0.200    |         |         |

| Detector Length(m)               | 2.400    |         |         |

| Number of stubs per layer        | 3000.000 |         |         |

|                                  | Layer 1  | Layer 2 | Layer 3 |

| R(m)                             | 0.250    | 0.375   | 0.525   |

| Phi(rad)                         | 0.075    | 0.113   | 0.158   |

| Searching range in phi (rad)     | 0.075    |         | 0.091   |

| (deg.)                           | 4.316    |         | 5.205   |

| (mm)                             | 18.834   |         | 47.691  |

| Search range in Z (mm)           | 66.667   |         | 80.000  |

| Total Layer Area (m^2)           | 3.770    |         | 7.917   |

|                                  |          |         |         |

| Number of Hits in searching area | 0.999    |         | 1.446   |

- For almost all 3000 stubs in Layer 2, on average a hit can be found in Layer 1 or Layer 3.

- About 90% of these pairs are not part of true tracks.

- When 3000 stubs/layer are sent to the stub pairing stage, there will be about 3000 pairs output to the tracking stage without significant reduction.

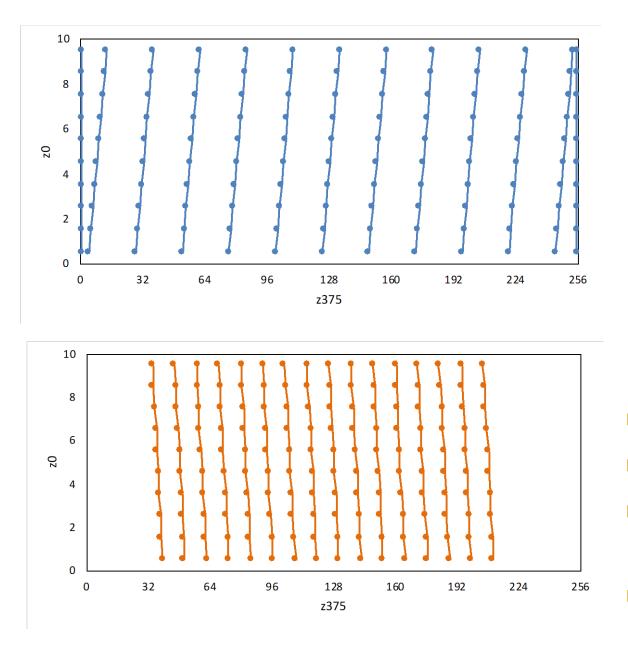

### Hits in the Hugh Transform Cells

- A hit is written into 10 z0 RAM blocks.

- The hits in Layer 1 and Layer 3 have different angles.

- The z coordinate of Layer 2, z375 is used to address all RAM block simultaneously.

- If an intersection of Layer 1 and Layer 3 hits are met, it might be a potential track segment.

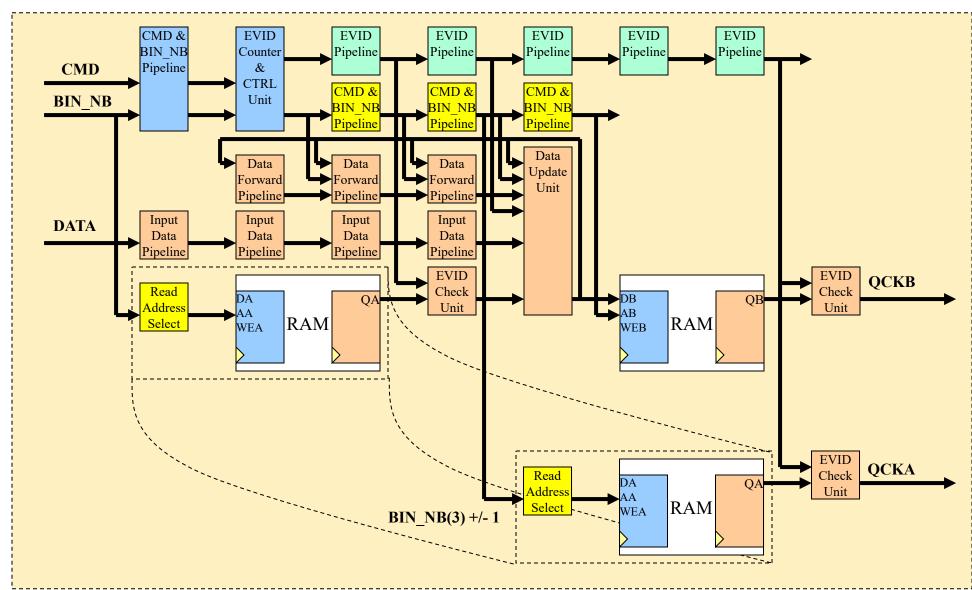

### Register-Like Block RAM Block Diagram

### Detailed Block Diagram

Boundary coverage is also supported during reading operations.