# Monolithic Active Pixel Matrix with Binary Counters (MAMBO) ASIC

Farah F. Khalid, *Member, IEEE*, Grzegorz W. Deptuch, *Senior Member, IEEE*, Alpana Shenai and Raymond J. Yarema, *Life Member, IEEE*

Abstract-Monolithic Active Matrix with Binary Counters (MAMBO) is a counting ASIC designed for detecting and measuring low energy X-rays from 6-12keV. Each pixel contains analogue functionality implemented with a charge preamplifier, CR-RC<sup>2</sup> shaper and a baseline restorer. It also contains a window comparator which can be trimmed by 4 bit DACs to remove systematic offsets. The hits are registered by a 12 bit ripple counter which is reconfigured as a shift register to serially output the data from the entire ASIC. Each pixel can be tested individually. Two diverse approaches have been used to prevent coupling between the detector and electronics in MAMBO III and MAMBO IV. MAMBO III is a 3D ASIC, the bottom ASIC consists of diodes which are connected to the top ASIC using µbump bonds. The detector is decoupled from the electronics by physically separating them on two tiers and using several metal layers as a shield. MAMBO IV is a monolithic structure which uses a nested well approach to isolate the detector from the electronics. The ASICs are being fabricated using the SOI 0.2µm OKI process, MAMBO III is 3D bonded at T-Micro and MAMBO IV nested well structure was developed in collaboration between OKI and Fermilab.

#### I. INTRODUCTION

THE combination of detector and signal processing electronics in each pixel is possible by using Silicon-on-Insulator (SOI) Technology. Unlike Monolithic Active Pixel Sensors (MAPS) in CMOS bulk process which offer limited signal processing capabilities and are restricted to the use of NMOS transistors in the active area, the SOI process has the advantage of advanced signal processing capabilities and the use of both NMOS and PMOS transistors. The  $0.2\mu m$  OKI SOI process is available via the SOIPIX collaboration led by KEK. It has a Buried Oxide (BOX) layer of 200nm, in a high resistivity substrate of 1 k $\Omega$ cm, n-type handle wafer. Detailed tests from previous designs in this process have led to the conclusion that the process exhibits problems related to capacitive coupling between the detector and electronics. The Monolithic Active Matrix with Binary Counters (MAMBO)

Manuscript received Nov 19, 2010. This manuscript has been authored by Fermi Research Alliance, LLC under Contract No. DE-AC02-07CH11359 with the U.S. Department of Energy. The authors are with the Fermi National Accelerator Laboratory, Batavia, Illinois 60510, USA (telephone: 630-840-8423; fax: 630-840-2950; e-mail: <a href="mailto:farah@fnal.gov">farah@fnal.gov</a>, <a href="mailto:depthone: depthone: 630-840, shenai@fnal.gov">depthone: 630-840, shenai@fnal.gov</a>, <a href="mailto:yarema@fnal.gov">yarema@fnal.gov</a>)

ASIC has been designed for detecting and measuring low energy X-Rays from 6keV – 12keV for applications such as transmission radiography, autoradiography and fluorescence X-Ray spectroscopy.

#### II. PIXEL ARCHITECTURE

Each pixel consists of a charge sensitive preamplifier, shaper, baseline restorer, window comparator, 4 bit trimming DACs and a 12 bit ripple counter which can be reconfigured as a shift register.

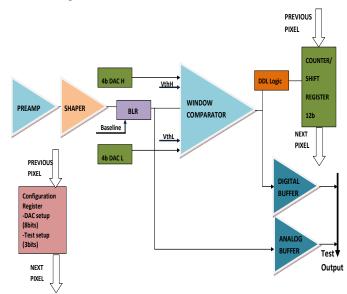

Each pixel can be configured to several operating modes and can be individually tested. The pixel block diagram is shown in Fig. 1.

Fig. 1. Pixel Block Diagram

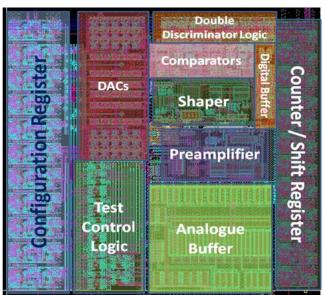

The pixel layout is shown in Fig. 2. Each pixel contains approximately 950 transistors. The primary aim of this design is ease of testability per pixel. The layout has not been optimized for area, in the final version of the ASIC once it is fully tested and characterized a significant part of the test control logic and the configuration register can be eliminated. The analog and digital buffers can also be removed. The area of the counter shift register can be further reduced by using a pseudorandom counter instead of a binary ripple counter. The

above modification would reduce the current pixel size from  $100 \mu m \times 100 \mu m$  to at least 75  $\mu m \times 75 \mu m$ .

Fig. 2 Pixel Layout

# III. IN-PIXEL ELECTRONICS

# A. Preamplifier, Shaper and Baseline Restorer

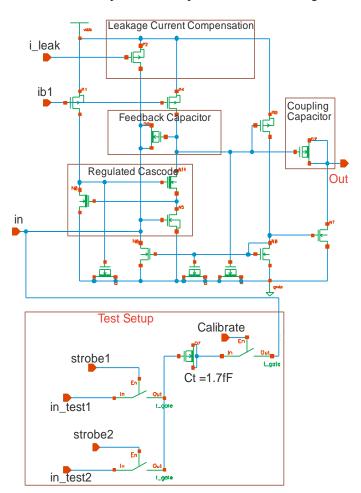

A single stage, single ended amplifier in a regulated cascode configuration is used as the charge preamplifier as shown in Fig. 3. It has a feedback capacitance of Cfp=5fF, an active feedback resistance and a coupling capacitance to the shaper Cc=35fF. The leakage current compensation circuit in the preamplifier can tolerate up to 200pA of current, realistic values are not expected to exceed a few pA.

The test setup includes a test capacitance of Ct =1.7fF connected on one end to the input through a switch which is ON for calibration and testing phase. Two transmission gates are connected on the other end of the test capacitance. These are connected to in\_test\_1 and in\_test\_2 and controlled by strobe1 and strobe2 signals respectively. The calibration circuit produces a pulse of small amplitude Vt, which applied to the test capacitor Ct generates short current pulses of well controlled charge (Qin = Ct × Vt) at the input of the CSA. The amplitude Vt is equal to the difference of voltage on in\_test\_1 and in\_test\_2.

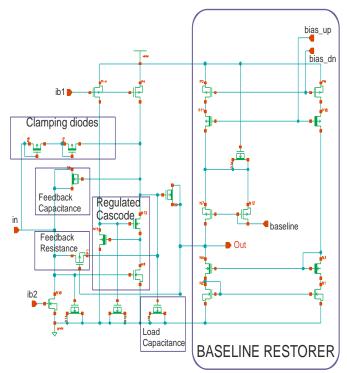

The shaping-filter has two integration stages. The first integration is still in the preamplifier, while the second separate stage provides a CR-RC type filtering of the signal and adds voltage gain. The overall degree of the shaping filter is CR-CR<sup>2</sup>. A regulated cascode design in the second stage is designed to provide replica of the DC voltage on the input for proper operation of the nonlinear pole-zero cancelation circuit. A compact design of the second stage was achieved as its transconductance is directly used in the realization of the desired transfer function. The transconductance element gm=6.5 $\mu$ S operates with a feedback capacitance of Cfs=3.5fF, an active feedback resistance of Rfs=28M $\Omega$  and the output has a load capacitance of Ch=25fF. Clamping diodes are used in

the feedback to enable a fast overload recovery. Although, a correct shaping of the signal is lost in case of large signals, the recovery to the baseline occurs swiftly. The ratio between the coupling capacitor Cc and the feedback capacitor Cfs sets the gain of the shaper equal to 10. The sensitivity of the preamplifier, shaper combination is 100 mV/1000 + holes. The equivalent noise charge is approximately 80e-. The input dynamic range is 500 + to 4000 + for a positive polarity p-on-n type detector.

A simple baseline restorer is used to reduce DC-level variations at the input of the comparators as shown in Fig. 4.

Fig. 3 Charge sensitive Preamplifier

Fig. 4 Shaper and Baseline restorer

#### B. Window Comparator and trimming DACs

The window comparator consists of two hysteresis comparators in parallel connected to a lower (VthL) and upper (VthH) threshold respectively, the offsets of the comparators can be independently adjusted by the trimming DACs. The double discriminator logic allows the energy windowing function. If VthL < Signal < VthH, then it is recorded as HIT.

# Hysteresis Comparator

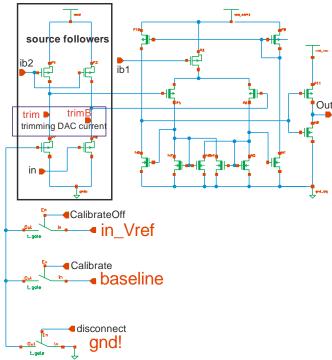

Source followers isolate the comparator from the shaper as shown in Fig. 5. One input of the discriminator is always connected to the shaper output. During normal operation the other input is connected to the reference voltage (in\_vref), when the comparator is being trimmed to cancel offsets, it is connected to the externally generated bias baseline and when the pixel is disabled or during analogue testing it is connected to ground.

Fig. 5 Hysteresis comparator

# Double discriminator logic

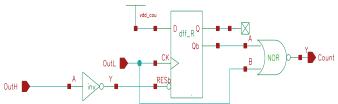

Fig. 6 Double discriminator logic

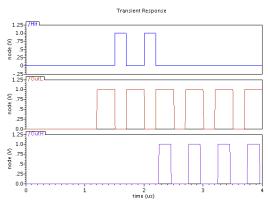

The double discriminator logic shown in Fig. 6 uses the output of the two comparators for further processing. The output of the lower threshold comparator behaves as a clock. The output of the upper threshold comparator behaves as a reset. If both the comparators fire, the hit is discarded. The Fig. 7 shows the output waveform. Only two hits out of total six are registered as a result of the energy windowing.

Fig. 7 Window comparator simulation results

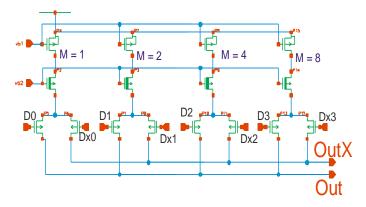

#### Current steering DACs

The current steering DAC consists of cascaded binary current mirrors arranged in conventional symmetrical common centroid geometry. The switches are also binary weighted so that all the current mirrors have equal loads as shown in Fig. 8. Matching is critical for monotonic performance of the DAC. The current can be steered either to the positive or negative terminal. The minimum current of 2nA is used; however this can be increased externally if the offset is more than a few tens of mV.

Fig. 8 Current Steering DAC

The output from the trimming DAC cancels the offset at the input of the differential pair of the amplifier.

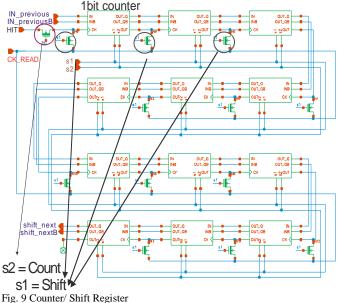

# C. Counter and Shift register

Counter/Shift register consists of a 12 bit ripple counter; the output of the double discriminator logic (DDL) is the clock for the counter. A switch disconnects the counter from the window comparator while shifting connecting the input of the first flip flop to the last flip flop from the previous pixel. An external clock CK\_READ is used for shifting data as shown in Fig. 9.

# D. Pixel operation modes and test electronics

Each pixel can be individually tested and calibrated with the aid of the pixel configuration register and test logic.

#### Pixel configuration

An 11 bit configuration register is used to setup the operation of each pixel. The data is input serially using the serial clk. It is then loaded onto a latch using the parallel load signal. 2 x 4bits are used for settings of the two trimming DACs. The rest 3 bits are used by test control logic to setup the pixel for the right mode of operation. 000 is used for normal operation and 111 to disable the pixel. 011 and 100 is used for calibrating the lower and upper DACs respectively. 001 is for analog calibration while 010 is for testing the counter. It also consists of a 3-8 bit decoder and additional combinatorial logic to control switches.

# Analog and digital buffer

The analogue buffer is used only for test purposes hence it is disconnected during normal operation. Only one pixel can be tested at a time, hence only one analogue buffer is enabled. The tail current of the buffer is disconnected when it is not in use such that the power consumption of the ASIC is minimized. Source followers are used to shift the voltage level of the signal to the operating range of the buffer amplifier. The buffer is a single stage amplifier with 10µA of tail current. It has a gain of about 50dB.

The output of either one of the comparators or the DDL is connected to a digital buffer to enable testing of the digital functionality of the ASIC.

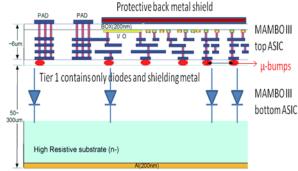

#### IV. MAMBO III

The T-Micro 3D integration process is used to bond the detector in the lower tier to the electronics in the upper tier. This separates the functions of charge generation and charge processing to two SOI layers, thus, eliminating the direct coupling paths. MAMBO III top and bottom ASIC contains a matrix of 44 x 44 pixels and occupies an area of 5mm x 5mm.

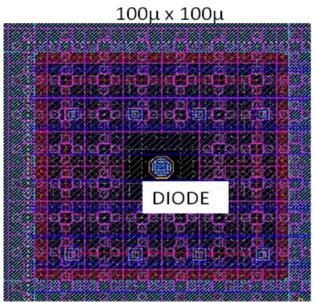

MAMBO III bottom ASIC pixel contains gated diodes; a layout of one element is shown in Fig. 10. The diode is encompassed by a ring of metall. By controlling the voltage of the metall layer any possible short between the adjacent diodes due to surface variation in doping and electrical conditions can be managed. A diode is build with a small p-plus region with a large buried P-well (BPW), almost the same size as the pixel to obtain a parallel electric field in active volume and avoid potential pockets that may alter charge transport.

Each pixel is  $100x100\mu m^2$  with a 5x5  $\mu m^2$  3D bump bond pad which has a 2x2  $\mu m^2$  3D bump bond contact. It is also effectively shielded to electrically isolate the detector from the electronics using metal layers 3 and 4.

Fig. 10 Diode Pixel

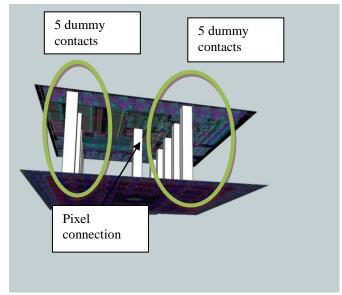

Each pixel has 11 connections, one diode connection from the bottom pixel to the preamplifier in the top pixel. The 10 dummy connections are added to increase the bonding density to satisfy process requirements for better yield. The 3D bonding process requires mechanical rigidity which is enhanced by using more contacts between the two ASICs and eventually epoxy underfill is used. The conceptual diagram of the 3D connection between the two pixels is shown in Fig. 11.

The bottom ASIC does not have any pads for wedge bonding or any other possibility of connecting to the external world. All connections are made using the micro bump bonds to the top ASIC.

Fig. 11 Conceptual diagram of the 3D bonded pixel

The top ASIC is back thinned. The silicon handle part is removed and through buried oxide (BOX) contacts, inserted at the fabrication of the front-end-of-line part, are exposed. By depositing and patterning metal on the back, all the pads are available on the surface. The through BOX contacts provide electrical connections to the post-processed pads on the surface as shown in Fig. 12.

Fig. 12 Cross sectional view of 3D bonded ASICs

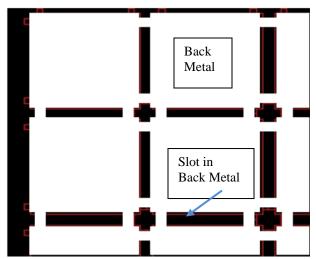

After the handle part of the wafer is removed, the transistors and sensitive nodes do not see a reference plane any more. Couplings through the BOX layer of 200nm from external environment and inter-components coupling may be a source of an excess noise in the system, thus the back metal was decided to be used as a shield to protect the transistors, as shown conceptually in Fig. 12 and in the layout in Fig. 13.

Fig. 13 Shielding per pixel using back metal

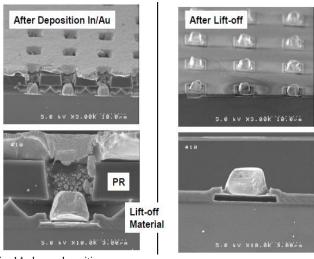

T-Micro uses an Au/In + adhesive underfill 3D bonding process. SEM images of the  $\mu$ bump deposition technique are shown in Fig. 14.

Fig. 14 µbump deposition

MAMBO III was submitted for fabrication in January 2010; the 2D ASICs were manufactured in May 2010, and due to technological problems with 3D  $\mu$ -bump bonding process, further process adjustments and repetition of  $\mu$ -bump deposition is currently being carried out at T-Micro.

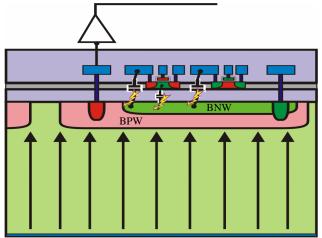

#### V. MAMBO IV

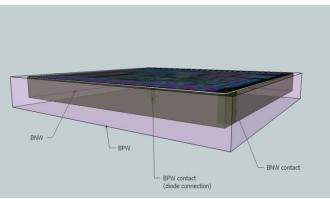

The nested well structure is shown in Fig. 15, it consists of a buried n-well (BNW) underneath all the electronics which acts as an AC ground to all electrical signals capacitively coupling to BNW. A deeper buried p-well (BPW) creates a homogenous electric field through the entire detector volume. This will enable us to once again exploit the advantages of the SOI process with a monolithic combination of the detector and electronics, having eliminated its negative impacts. The main drawback of the nested well structure is the significant increase in diode capacitance as the entire BPW is now the

collecting diode. This capacitance is strongly dependent on the size of the designed pixel, namely on the area of the deep BPW and BNW and the combination of the doping energies and the doses of Boron in the implanting of the deep BPW. In the current layout the diode capacitance is approximately equal to 2pF; in the final design it is estimated that reducing the size of the pixel and further optimizing the conditions of doping of the implant will reduce this capacitance to 1 pF or even

Fig. 15 Nested well conceptual view

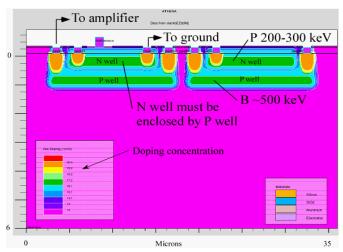

The nested well structure was collaboratively developed by Fermilab and OKI Semiconductor Ltd. Fig. 16 shows a Silvaco simulation of the nested well structure using implantation energies for Boron doping of 500keV and Phosphorus doping between 200-300keV.

Fig. 16 Silvaco simulation of nested well

Each pixel in MAMBO IV has the same electronics as MAMBO III but the pixel size is increased to  $105 \times 105 \mu m^2$  to meet design rule constraints of minimum separation between adjacent buried p-wells.

Fig. 17 Model of nested well structure

MAMBO IV ASIC contains a matrix of 41 x 42 pixels and occupies an area of 5mm x 5mm. MAMBO IV was submitted for manufacture in Aug 2010 and is currently being fabricated.

# VI. CONCLUSION

MAMBO is a counting ASIC with full testing capability of each pixel. Various methods are explored to avoid coupling between detector and the in-pixel electronics. MAMBO III is a 3D ASIC with the detector and electronics on two separate tiers. The detector is shielded effectively using all available metal layers. MAMBO IV is a fully monolithic ASIC with the high resistivity substrate behaving as the detector. A nested well approach was developed and is used to shield the detector from the electronics thereby eliminating any coupling from the CMOS circuitry into the diodes in the substrate

# ACKNOWLEDGMENT

The authors would like to thank the SOIPIX collaboration for the availability of OKI SOI MPW runs, T-Micro for 3D ASIC bonding and OKI Semiconductor Ltd. for co-developing the nested well structure.

# REFERENCES

- [1] Deptuch, G. "Monolithic Pixel Detectors in deep submicron SOI process", *Nucl. Inst Meth A*, vol. 623,iss. 1, pp. 183-185, Nov 2010.

- [2] SOIPIX collaboration: <a href="http://rd.kek.jp/project/SOI/">http://rd.kek.jp/project/SOI/</a>

- [3] Khalid, F. F., Deptuch, G., Shenai, A., Yarema, R., "Monolithic Active Pixel Matrix with binary counters (MAMBO III)", *Proceedings of Science* (VERTEX 2010) 029

- [4] Motoyoshi, M., Kamibayashi, K. Bonkohara, M. and Koyonagi, M., "Current and future 3 dimensional LSI technologies", *Technical Digest of the Intenational 3D system integration conference* (2007)

- [5] De Geronimo, G.; Fried, J.; O'Connor, P.; Radeka, V.; Smith, G.C.; Thorn, C.; Bo Yu; "Front-end ASIC for a GEM based time projection chamber", *IEEE Trans. on Nuclear Sci.* 2004, Vol. 51, p. 1312

- [6] Gramegna, G. Oapos, O'Connor, P, Rehak, P. Hart, S. "Low-noise CMOS preamplifier-shaper for silicon drift detectors," *IEEE Trans. Nucl. Sci.*, vol. 44, no. 3, pp.385-388, Jun. 1997.