FERMILAB-Conf-99/179

# **SUMAC: A Monitor and Control Tree for Multi-FPGA Systems**

Mingshen Gao For the BTeV Collaboration

Fermi National Accelerator Laboratory P.O. Box 500, Batavia, Illinois 60510

July 1999

Published Proceedings of the *11th IEEE NPSS Real Time Conference*, Santa Fe, New Mexico, June 14-18, 1999

Operated by Universities Research Association Inc. under Contract No. DE-AC02-76CH03000 with the United States Department of Energy

## Disclaimer

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, expressed or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

## Distribution

Approved for public release; further dissemination unlimited.

#### **Copyright Notification**

This manuscript has been authored by Universities Research Association, Inc. under contract No. DE-AC02-76CHO3000 with the U.S. Department of Energy. The United States Government and the publisher, by accepting the article for publication, acknowledges that the United States Government retains a nonexclusive, paid-up, irrevocable, worldwide license to publish or reproduce the published form of this manuscript, or allow others to do so, for United States Government Purposes.

## <u>SUMAC: A Monitor and Control Tree</u> <u>for Multi-FPGA Systems</u>

Mingshen Gao FermiLab, P.O.Box 500, Batavia, IL 60510 For Btev collaboration

The BTeV pixel trigger is a data acquisition system capable of finding tracks and vertices in real time in the BTeV pixel detector array. The trigger uses some 3000 processing elements (DSPs) arranged in three processing levels to handle a raw data rate of nearly 100 Gigabytes per second and bring the trigger rate down to 10 KHz.

The trigger system has more than 6000 programmable elements, including Field Programmable Logic Arrays (FPGAs), microprocessors (DSPs, interface to the monitor and control tree through FPGAs), and others. Sumac (Serial Utility Monitor and Control tree) is used for configuring and monitoring of these devices. Its primary function is the downloading of FPGA bit streams, microprocessor programs, chip configurations, and test data. In addition, remote cpus and other devices can send messages and status back to the host. The Sumac system is capable of handling several thousand remote devices from a single host PC. Because it stores configuration data in local flash eeproms, it will be capable of achieving a complete system reboot in less than 1 second.

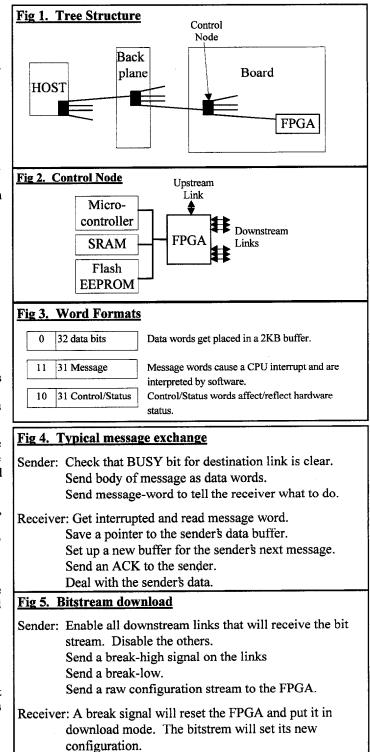

The Sumac system is a tree hierarchy connected via high-speed serial links. Typically each board in the system will have a control node which accepts a single upstream serial link and fans out to as many as 32 downstream links. The downstream links can connect to FPGAs or to other control nodes for further fanout.

Short links that connect devices on the same board or backplane are implemented as 20 MHz synchronous serial links. Longer links that connect host to backplane are implemented as 12.5 MHz asynchronous serial links.

The serial link sends and receives 33-bit words. Figure 3 shows the three basic word formats. Data words contain user-defined data. Typically, these get placed into a local buffer until a message word is received that tells the software how to deal with them.

Message words contain a 31-bit payload that is defined by the software. Message words cause an interrupt to the CPU. Each message word that is sent must be acknowledged before a new message word can be sent.

Control/Status words are low-level hardware words. Typically, control words are sent downstream and affect the hardware state of the receiver. Status words are typically sent upstream and are used to indicate the current hardware status. They can be sent periodically or under CPU control.

Bit 29 of the Control/Status word is reserved to indicate a message acknowledge. When this bit is received, it clears the BUSY bit, and tells the CPU that it can send another message.

In addition to the 33-bit serial format, each control node can transmit a raw bit stream that can be used to configure the receiving device. Figure 5 shows the flow for configuring an FPGA.

Control nodes can keep data files locally so that the host does not have to re-load them on each reboot. The control node accepts commands to manipulate and download files. It also interprets a simple scripting language so that it can configure an entire board with only a single command from an upstream node.

The control node also accepts commands from downstream nodes to pass messages upstream. This allows remote devices to send occasional text messages to the host to indicate error conditions or status changes. This feature will be accessible to user-level programs running in remote CPUs as printf-like system calls.

#### Serial Link Encoding

Sumac links that run between boxes use RS-485 differential signaling at 12.5MHz. A serial encoding scheme is needed that embeds a clock reference into the data, and maintains a reasonable DC bias. For Sumac, the 33-bit word is broken into eight "nibbles". The first nibble is 5 bits; the other seven are 4 bits each. The nibbles are then encoded using 5B/6B or 4B/5B NRZI encoding.

NRZI (Non-Return to Zero Inverted) encoding uses a transition to indicate a 1, and the absence of a transition to indicate a 0. The 5B/6B encoding inserts an extra bit into each nibble to insure that there is a transition (1) at least once every 4 bits. The table shows how each combination is encoded. In addition to the 32 data encodings, there are also codings for a FILL word which is sent whenever there is no data to send, and a SYNC word which is sent at link startup or when an error is detected. Any code not in the table is considered an error.

For 4B/5B encoding, a subset of the 5B/6B is used. Only the lowest 5 encoded bits are used to represent a 4bit nibble.

## Special states

#### Break

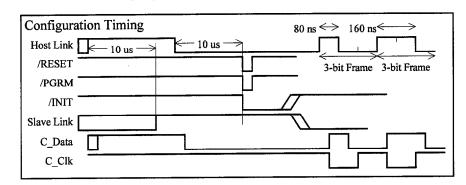

If the Host holds the serial link high for 10 microseconds, the Slave enters Break-High state. In this state, the Slave's control processor is allowed to operate independently and attempt to boot without the host. The Slave responds to a Break-High by driving its own serial link high. This state is also entered if the control-link cable is disconnected.

#### Reset

If the Host holds the serial link low for 10 microseconds (Break-Low), hardware reset is asserted on the slave node. This will reset the FPGA and Re-start the Slave's control processor. The Slave responds by driving its serial link low.

#### Config

If the Host sends a Break-High followed by a Break-Low, then the Slave is reset, and its FPGA is cleared and prepared to accept a new bitstream configuration. Each bit of configuration data is sent to the FPGA as a 3-bit frame on the serial link. The frame consists of a high start bit followed by a data bit, followed by a low stop bit. For each frame, the FPGA configuration clock (C\_CLK) is cycled once, and a bit is written into the FPGA on the rising edge.

| Decoding Map, 6B to 5B |              |      |            |     |     |     |            |      |            |

|------------------------|--------------|------|------------|-----|-----|-----|------------|------|------------|

|                        | Lower 3 bits |      |            |     |     |     |            |      |            |

|                        |              | 000  | 001        | 010 | 011 | 100 | 101        | 110  | 111        |

|                        | 000          | -    | -          | -   | -   | -   | -          | -    | -          |

| 2                      | 001          | -    | 4          | -   | 5   | -   | 6          | -    | 7          |

| E I                    | 010          | -    | 8          | 0   | 9   | -   | Α          | 1    | B          |

| 3 Bits                 | 011          | -    | С          | 2   | D   | -   | Ε          | 3    | F          |

|                        | 100          | Sync | -          | -   | -   | -   | -          | -    | -          |

| ۱ğ.                    | 101          | -    | 14         | -   | 15  | -   | 16         | Fill | 17         |

| Upper                  | 110          | -    | 18         | 10  | 19  | -   | 1 <b>A</b> | 11   | 1 <b>B</b> |

|                        | 111          | -    | 1 <b>C</b> | 12  | 1D  | -   | 1E         | 13   | 1F         |

|                        | L            |      |            |     |     |     |            |      |            |

#### Sync

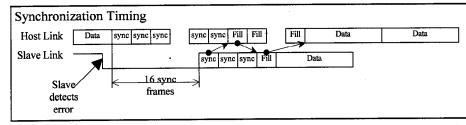

If the slave detects an error of any kind, it drives its output link low, and enters the Sync state. If the Host detects this or any other error, it enters the sync state and begins sending Sync words. When the slave has detected 16 contiguous sync words, it begins sending sync words on its output link. When the host detects this, it begins sending Fill words. When the Slave detects Fill words, then it begins sending Fill words. At this point, the links are synchronized, and data words can be sent.

| Q0= B0 ? B1 : B3                                  |

|---------------------------------------------------|

| $\tilde{Q}_{1}=B2$                                |

| Q2 = B0 * B3                                      |

| Q3 = B0 * B4                                      |

| O4= B5                                            |

| <b>e</b> . <u></u>                                |

| Encoding Equations 5Q to 6B                       |

| B0 = Q3 + Q2                                      |

|                                                   |

|                                                   |

| B1 = /Q3 * /Q2 + Q0                               |

| B1= /Q3 * /Q2 + Q0<br>B2= Q1                      |

| B1= /Q3 * /Q2 + Q0<br>B2= Q1<br>B3= Q2 + /Q3 * Q0 |

| B1= /Q3 * /Q2 + Q0<br>B2= Q1                      |

Decoding equations 6B to 5Q

| Encoding Table, 5B to 6B |        |         |  |  |  |  |  |

|--------------------------|--------|---------|--|--|--|--|--|

| Nibble                   | Binary | Encoded |  |  |  |  |  |

| 0                        | 00000  | 010010  |  |  |  |  |  |

| 1                        | 00001  | 011010  |  |  |  |  |  |

| 2                        | 00010  | 010110  |  |  |  |  |  |

| 3                        | 00011  | 011110  |  |  |  |  |  |

| 4                        | 00100  | 001001  |  |  |  |  |  |

| 5                        | 00101  | 001011  |  |  |  |  |  |

| 6                        | 00110  | 001101  |  |  |  |  |  |

| 7                        | 00111  | 001111  |  |  |  |  |  |

| 8                        | 01000  | 010001  |  |  |  |  |  |

| 9                        | 01001  | 010011  |  |  |  |  |  |

| A                        | 01010  | 010101  |  |  |  |  |  |

| В                        | 01011  | 010111  |  |  |  |  |  |

| С                        | 01100  | 011001  |  |  |  |  |  |

| D                        | 01101  | 011011  |  |  |  |  |  |

| Е                        | 01110  | 011101  |  |  |  |  |  |

| F                        | 01111  | 011111  |  |  |  |  |  |

| 10                       | 10000  | 110010  |  |  |  |  |  |

| 11                       | 10001  | 111010  |  |  |  |  |  |

| 12                       | 10010  | 110110  |  |  |  |  |  |

| 13                       | 10011  | 111110  |  |  |  |  |  |

| 14                       | 10100  | 101001  |  |  |  |  |  |

| 15                       | 10101  | 101011  |  |  |  |  |  |

| 16                       | 10110  | 101101  |  |  |  |  |  |

| 17                       | 10111  | 101111  |  |  |  |  |  |

| 18                       | 11000  | 110001  |  |  |  |  |  |

| 19                       | 11001  | 110011  |  |  |  |  |  |

| 1A                       | 11010  | 110101  |  |  |  |  |  |

| 1 <b>B</b>               | 11011  | 110111  |  |  |  |  |  |

| 1C                       | 11100  | 111001  |  |  |  |  |  |

| 1D                       | 11101  | 111011  |  |  |  |  |  |

| 1E                       | 11110  | 111101  |  |  |  |  |  |

| 1F                       | 11111  | 111111  |  |  |  |  |  |

| SYNC                     | Sync   | 100000  |  |  |  |  |  |

| FILL                     | Fill   | 101110  |  |  |  |  |  |

|                          |        | •       |  |  |  |  |  |