Paper Number: P08

#### Vertically Integrated Edgeless Photon Imaging Camera

Farah Fahim<sup>1</sup>, Grzegorz Deptuch<sup>1</sup>, Alpana Shenai<sup>1</sup>, Piotr Maj<sup>2</sup>, Piotr Kmon<sup>2</sup>, Paweł Grybos<sup>2</sup>, Robert Szczygieł<sup>2</sup>, D. Peter Siddons<sup>3</sup>, Abdul Rumaiz<sup>3</sup>, Anthony Kuczewski<sup>3</sup>, Joseph Mead<sup>3</sup>, Rebecca Bradford<sup>4</sup>, John Weizeorick<sup>4</sup> <sup>1</sup> Fermi National Accelerator Laboratory, USA <sup>2</sup> AGH-UST, Krakow, Poland <sup>3</sup> Brookhaven National Laboratory, USA <sup>4</sup> Argonne National Laboratory, USA

Abstract: The Vertically Integrated Photon Imaging Chip - Large, (VIPIC-L), is a large area, small pixel ( $65\mu$ m), 3D integrated, photon counting ASIC with zero-suppressed or full frame dead-time-less data readout. It features data throughput of 14.4 Gbps per chip with a full frame readout speed of 56kframes/s in the imaging mode. VIPIC-L contain 192 x 192 pixel array and the total size of the chip is 1.248cm x 1.248cm with only a 5 $\mu$ m periphery. It contains about 120M transistors. A 1.3M pixel camera module will be developed by arranging a 6 x 6 array of 3D VIPIC-L's bonded to a large area silicon sensor on the analog side and to a readout board on the digital side. The readout board hosts a bank of FPGA's, one per VIPIC-L to allow processing of up to 0.7 Tbps of raw data produced by the camera.

Keywords: Stacked Imagers, low noise analog front-end, camera system.

# 1. Introduction

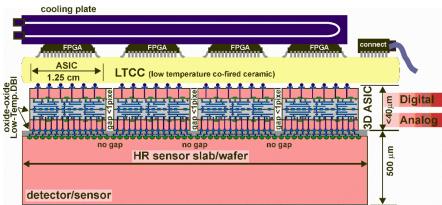

A prototype vertically integrated photon imaging readout integrated circuit (VIPIC1) was designed for X-ray Photon Correlation Spectroscopy experiments at synchrotron radiation sources [<sup>i</sup>]. This pixel detector utilized 3D stacking technology with both the Cu-Cu thermo-compression [<sup>ii</sup>] and the Cu DBI [<sup>iii</sup>] bonding which yielded operational devices. The ROICs with a pixel pitch of 80  $\mu$ m were bonded to silicon pixelated sensors with the measured noise corresponding to 39 e- and 70 e-, respectively for the readout channels that were not connected and connected to the sensor diodes. The conversion gain varied from 43 to 52  $\mu$ V/e- as a function of the bias current in the front-end block. Essentially all the pixels on a small prototype were operational [<sup>iv</sup>]. The next step in this development process aims at creating a large camera module as shown in Figure 1, with an array of large area (> 1cm<sup>2</sup>), small pixel (65 $\mu$ m) 3D bonded pixelated ROICs connected to a large area pixelated sensor on one end and a readout board on the other end. The aim of the development is to create a large area, gapless camera module.

The Vertically Integrated Photon Imaging Chip- Large (VIPIC-L) is a large area, edgeless, vertically integrated analog and a digital 3D stacked ROIC.

This manuscript has been authored by Fermi Research Alliance, LLC under Contract No. DE-AC02-07CH11359 with the U.S. Department of Energy, Office of Science, Office of High Energy Physics

Figure 1. Single module of 3D integrated edgeless camera

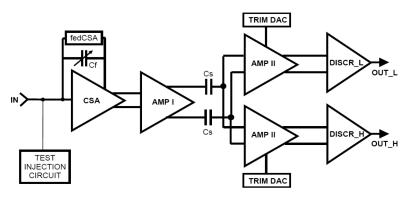

# 2. VIPIC Analog Tier

A full custom analog pixel is connected to a sensor pixel of the same size on one side, and on the other side it has approximately 40 connections to the digital pixel. Each pixel in the analog tier contains a signal processing chain which includes a charge sensitive amplifier with sensor leakage current compensation, followed by a two stage shaping filter and a window discriminator. Additionally, two 7-bit trimming Digital to Analog Converters (DAC) are used to remove systematic offsets in the comparators in every pixel as shown in Figure 2. The VIPIC-L has no peripheral functional blocks, and hence the active area extends to the edge of the detector.

Figure 2 Analog Pixel Block diagram

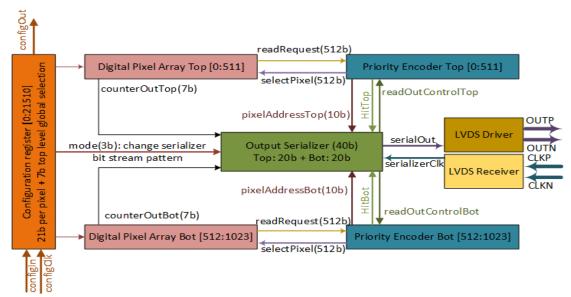

# 3. VIPIC Digital Tier

The Digital ASIC consists of approximately 100 million transistors and 1.5 million intertier connections to the Analog ASIC. The ASIC is subdivided into a 6 x 6 array of an indivisible functional unit (sub-chip) [ $^{v}$ ]. A sub-chip is a grouping of 1024 pixels, which allows for adequate area to contain the hit processing logic of all the pixels along with a priority encoder, an output serializer, LVDS drivers and receivers, as well as a 21,510-bit serial configuration register for trimming and setup of the analog pixels as shown in Figure 3.

Figure 3. Digital sub-chip functionality

#### 4. VIPIC Readout Board

Each ASIC has 720 bump-bond I/O connections, on the back of the digital tier to the ceramic PCB. All the analog tier power and biasing is conveyed through the digital tier from the PCB. The detector module is a composite of three rafts, each raft containing a 2 x 6 array of VIPIC-L chips bonded to a monolithic p-in-n diode pixel array as shown in Figure 4. Each VIPIC chip has 36 LVDS readout ports. Routing 36 x 12 such signals off the raft is not practical hence each VIPIC chip has a small FPGA to serve as a data concentrator, reducing the wiring to 12 high-speed serial links. Since significant power dissipation is anticipated, a water-cooled copper block is added which is thermally connected to the FPGA packages.

Figure 4. Module test board with 3 rafts each containing 2 x 6 array of VIPIC-L

# 5. Conclusions

The ROICs have been manufactured in GF130nm process and the 3D stacking process is currently underway.

#### REFERENCES

<sup>i</sup> Deptuch, G.W.; Carini, G.; Grybos, P.; Kmon, P.; Maj, P.; Trimpl, M.; Siddons, D.P.; Szczygiel, R.; Yarema, R., "Design and Tests of the Vertically Integrated Photon Imaging Chip," in Nuclear Science, IEEE Transactions on , vol.61, no.1, pp.663-674, Feb. 2014

<sup>ii</sup> R. S. Patti, "Three-dimensional integrated circuits and the future of system-on-chip designs," *Proc. IEEE*, vol. 94, no. 6, pp. 1214–1224, Jun. 2006.

<sup>III</sup> P. Enquist, "Scalable direct bond technology and applications driving adoption," in *Proc. IEEE Int. 3D Syst. Integr. Conf. (3DIC)*, Jan./Feb. 2012, pp. 1–5.

<sup>iv</sup> Deptuch, G.W., Carini, G., Enquist, P., Gryboś, P., Holm, S., Lipton, R., Maj, P., Patti, R., Siddons, D.P., Szczygieł, R. and Yarema, R., 2016. Fully 3-D integrated pixel detectors for X-Rays. *IEEE Transactions on Electron Devices*, *63*(1), pp.205-214.

<sup>v</sup> Fahim, Farah, Grzegorz W. Deptuch, James R. Hoff, and Hooman Mohseni. "Design Methodology: Edgeless 3D ASICs with complex in-pixel processing for Pixel Detectors." In SPIE Nanoscience+ Engineering, pp. 95550M-95550M. International Society for Optics and Photonics, 2015.